Part Number: LMK04828

Other Parts Discussed in Thread: LMX2594, LMK04832,

Hi All,

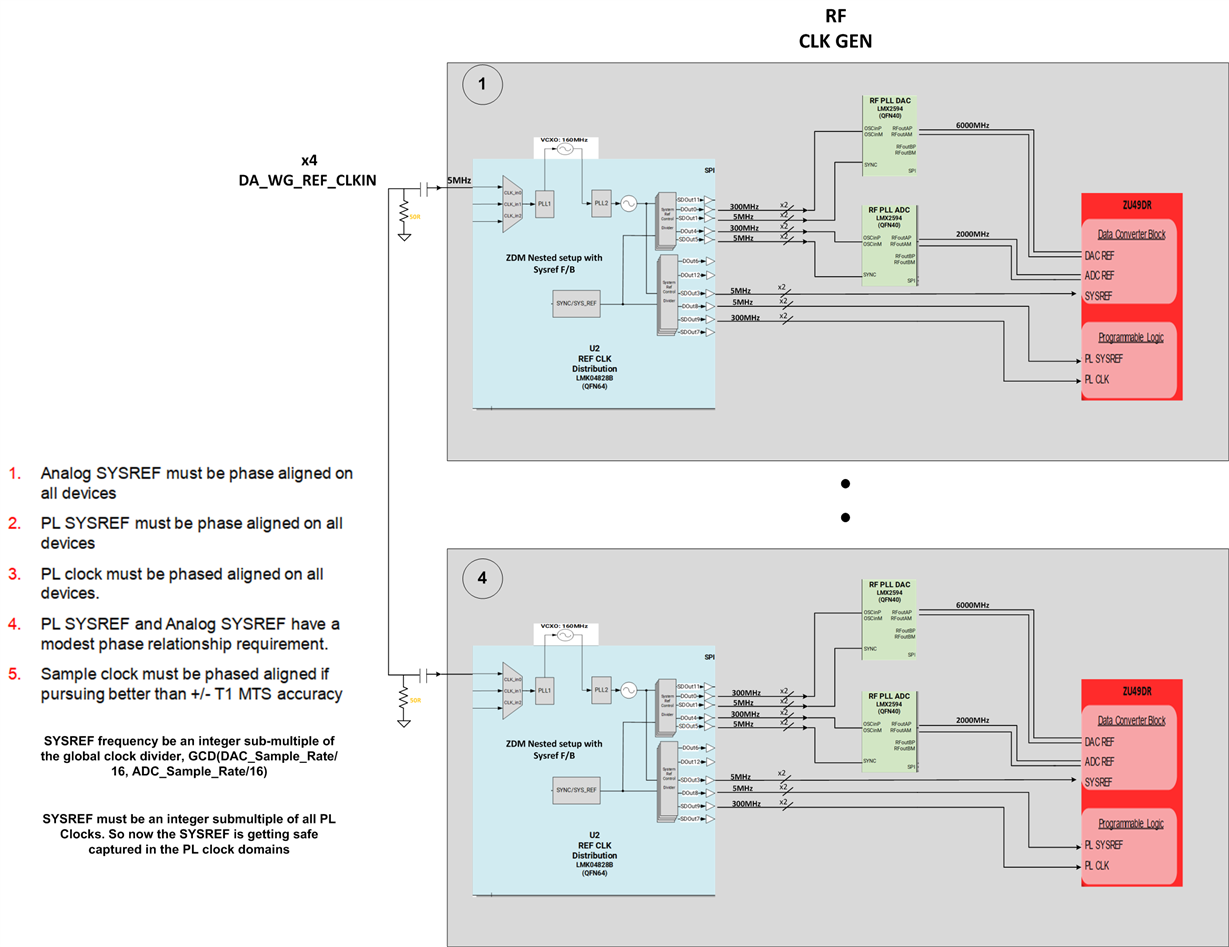

Could someone validate the clock scheme used for Multiple RFSoC synchronization

Will i be able to achieve <5 degree phase variation for all clock inputs across each RFSoC ?