Other Parts Discussed in Thread: LMK04826

I'm working on migrating a design with an existing PCB from LMK04826B to LMK04832. The board was working properly prior to replacing the PLL. Our source code has been updated to match the changes in the register map of the PLL, but it looks like we've missed something as I'm not getting any SYSREF signal on any of the SCLK outputs.

Some troubleshooting I've attempted:

- Tried both continuous and pulser output from the SYSREF_MUX, neither shows up at the SCLK outputs

- Tried switching the SCLK outputs to device clock via the CLKoutY_SRC_MUX, which works fine and outputs a clock signal

- Tried toggling SCLKX_Y_POL for the SCLK output, which works and causes the output to toggle

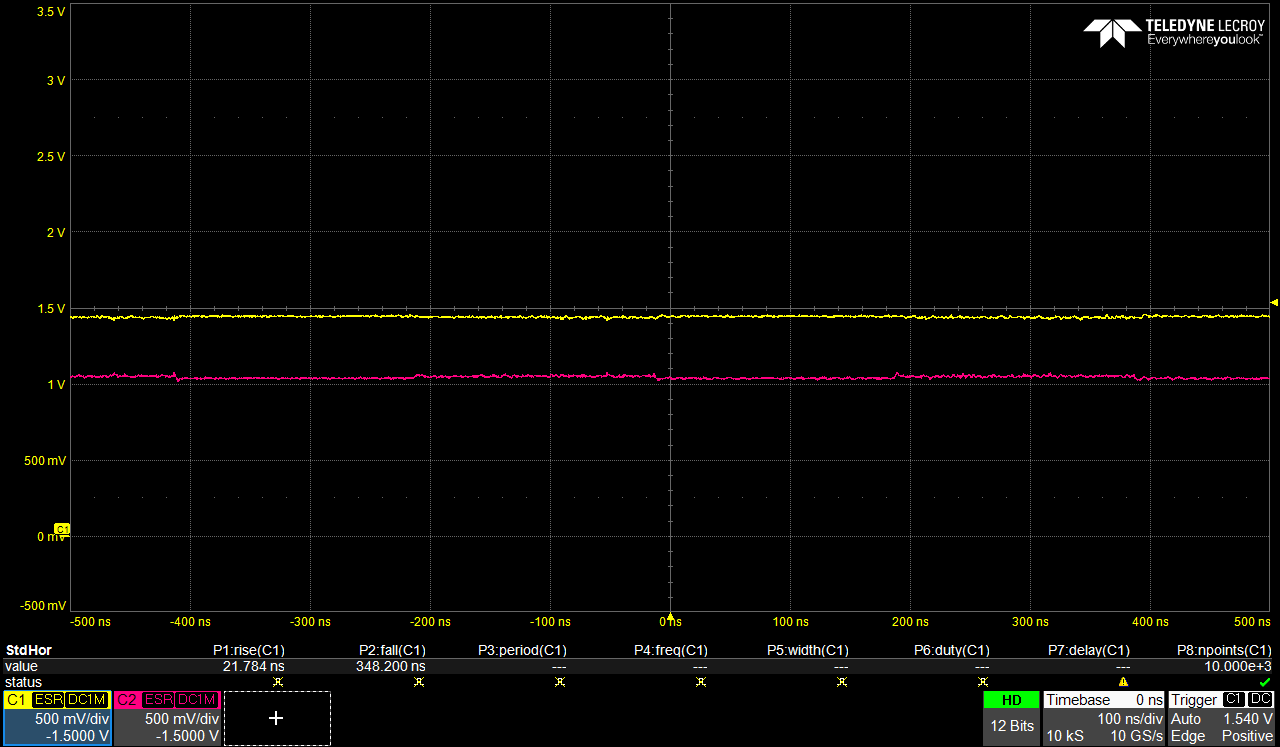

- Tried measuring the SYSREF_DIV clock via OSCout, using FB_MUX == SYSREF_DIV and OSCout_MUX == FB_MUX. This shows correct signal, 2.5 MHz with 50% duty cycle- Tried enabling/disabling parts of the SCLK signal path (DDLY, analog delay, etc), but none of the changes result in SYSREF output

Given that I've verified that SYSREF_DIV is OK via OSCout, and that the signal path from SCLKX_Y_POL and out to the PCB is OK by toggling the polarity, I'm assuming it must be something in between that stops the signal? SYSREF_CLR is zeroed when I'm doing these measurements.

The two PLLs both signal lock detect. I'm using a 10 MHz reference into PLL1, which controls a 100 MHz VCXO. PLL2 goes from 100 MHz to 2.5 GHz. PLL1 uses SYSREF_DIV as feedback, PLL2 uses local feedback via prescaler. SYSREF_DIV divides by 1000 to get 2.5 MHz. The outputs where I want SYSREF output are CLKout3, CLKout9 and CLKout13.

I've attached text files containing a readout of the register map, plus a parsed version where I've extracted the values of individual fields in the registers for easier reading.

0x000 0x10 0x001 0x00 0x002 0x00 0x003 0x06 0x004 0x63 0x005 0xD1 0x006 0x70 0x007 0x00 0x008 0x00 0x009 0x00 0x00A 0x00 0x00B 0x00 0x00C 0x51 0x00D 0x04 0x100 0x0A 0x101 0x00 0x102 0x00 0x103 0x00 0x104 0x34 0x105 0x00 0x106 0x08 0x107 0x01 0x108 0x08 0x109 0x00 0x10A 0x00 0x10B 0x00 0x10C 0x20 0x10D 0x00 0x10E 0x08 0x10F 0x11 0x110 0x08 0x111 0x00 0x112 0x00 0x113 0x00 0x114 0x10 0x115 0x00 0x116 0x08 0x117 0x11 0x118 0xFA 0x119 0x00 0x11A 0x00 0x11B 0x00 0x11C 0x34 0x11D 0x00 0x11E 0x08 0x11F 0x01 0x120 0x01 0x121 0x00 0x122 0x60 0x123 0x00 0x124 0x20 0x125 0x00 0x126 0x08 0x127 0x44 0x128 0x08 0x129 0x0A 0x12A 0x80 0x12B 0x50 0x12C 0x10 0x12D 0x00 0x12E 0x01 0x12F 0x00 0x130 0x01 0x131 0x00 0x132 0x60 0x133 0x00 0x134 0x20 0x135 0x00 0x136 0x08 0x137 0x44 0x138 0x18 0x139 0x03 0x13A 0x03 0x13B 0xE8 0x13C 0x00 0x13D 0x08 0x13E 0x00 0x13F 0x0D 0x140 0x00 0x141 0x80 0x142 0x00 0x143 0x50 0x144 0xFF 0x145 0x00 0x146 0x00 0x147 0x1A 0x148 0x0B 0x149 0x0B 0x14A 0x02 0x14B 0x16 0x14C 0x00 0x14D 0x00 0x14E 0x00 0x14F 0x7F 0x150 0x09 0x151 0x02 0x152 0x00 0x153 0x00 0x154 0x04 0x155 0x00 0x156 0x04 0x157 0x00 0x158 0x96 0x159 0x00 0x15A 0x01 0x15B 0x14 0x15C 0x3F 0x15D 0xFF 0x15E 0x1E 0x15F 0x3B 0x160 0x00 0x161 0x01 0x162 0xA4 0x163 0x00 0x164 0x00 0x165 0x05 0x166 0x00 0x167 0x00 0x168 0x05 0x169 0x59 0x16A 0x3F 0x16B 0xFF 0x16C 0x00 0x16D 0x00 0x16E 0x06 0x16F 0x20 0x170 0xA8 0x171 0xAA 0x172 0x02 0x173 0x0F 0x174 0x00 0x175 0x00 0x176 0x00 0x177 0x00 0x178 0x40 0x179 0x00 0x17A 0x18 0x17B 0x77 0x17C 0x15 0x17D 0x33 0x17E 0x00 0x17F 0x05 0x180 0x80 0x181 0x00 0x182 0x00 0x183 0x05 0x184 0x50 0x185 0xAF 0x186 0x00 0x187 0x00 0x188 0x41

Register 0x100 = 0x0A

DCLK0_1_DIV[7:0] 10

Register 0x101 = 0x00

DCLK0_1_DDLY[7:0] 0

Register 0x102 = 0x00

CLKout0_1_PD 0

CLKout0_1_ODL 0

CLKout0_1_IDL 0

DCLK0_1_DDLY_PD 0

DCLK0_1_DDLY[9:8] 0

DCLK0_1_DIV[9:8] 0

Register 0x103 = 0x00

Reserved == 1 0

CLKout0_SRC_MUX 0 == Device Clock

DCLK0_1_PD 0

DCLK0_1_BYP 0

DCLK0_1_DCC 0

DCLK0_1_POL 0

DCLK0_1_HS 0

Register 0x104 = 0x34

CLKout1_SRC_MUX 1 == SYSREF

SCLK0_1_PD 1

SCLK0_1_DIS_MODE 1

SCLK0_1_POL 0

SCLK0_1_HS 0

Register 0x105 = 0x00

SCLK0_1_ADLY_EN 0

SCLK0_1_ADLY 0

Register 0x106 = 0x08

SCLK0_1_DDLY 8

Register 0x107 = 0x01

CLKout1_FMT 0

CLKout0_FMT 1

Register 0x108 = 0x08

DCLK2_3_DIV[7:0] 8

Register 0x109 = 0x00

DCLK2_3_DDLY[7:0] 0

Register 0x10A = 0x00

CLKout2_3_PD 0

CLKout2_3_ODL 0

CLKout2_3_IDL 0

DCLK2_3_DDLY_PD 0

DCLK2_3_DDLY[9:8] 0

DCLK2_3_DIV[9:8] 0

Register 0x10B = 0x00

Reserved == 1 0

CLKout2_SRC_MUX 0 == Device Clock

DCLK2_3_PD 0

DCLK2_3_BYP 0

DCLK2_3_DCC 0

DCLK2_3_POL 0

DCLK2_3_HS 0

Register 0x10C = 0x20

CLKout3_SRC_MUX 1 == SYSREF

SCLK2_3_PD 0

SCLK2_3_DIS_MODE 0

SCLK2_3_POL 0

SCLK2_3_HS 0

Register 0x10D = 0x00

SCLK2_3_ADLY_EN 0

SCLK2_3_ADLY 0

Register 0x10E = 0x08

SCLK2_3_DDLY 8

Register 0x10F = 0x11

CLKout3_FMT 1

CLKout2_FMT 1

Register 0x110 = 0x08

DCLK4_5_DIV[7:0] 8

Register 0x111 = 0x00

DCLK4_5_DDLY[7:0] 0

Register 0x112 = 0x00

CLKout4_5_PD 0

CLKout4_5_ODL 0

CLKout4_5_IDL 0

DCLK4_5_DDLY_PD 0

DCLK4_5_DDLY[9:8] 0

DCLK4_5_DIV[9:8] 0

Register 0x113 = 0x00

Reserved == 1 0

CLKout4_SRC_MUX 0 == Device Clock

DCLK4_5_PD 0

DCLK4_5_BYP 0

DCLK4_5_DCC 0

DCLK4_5_POL 0

DCLK4_5_HS 0

Register 0x114 = 0x10

CLKout5_SRC_MUX 0 == Device Clock

SCLK4_5_PD 1

SCLK4_5_DIS_MODE 0

SCLK4_5_POL 0

SCLK4_5_HS 0

Register 0x115 = 0x00

SCLK4_5_ADLY_EN 0

SCLK4_5_ADLY 0

Register 0x116 = 0x08

SCLK4_5_DDLY 8

Register 0x117 = 0x11

CLKout5_FMT 1

CLKout4_FMT 1

Register 0x118 = 0xFA

DCLK6_7_DIV[7:0] 250

Register 0x119 = 0x00

DCLK6_7_DDLY[7:0] 0

Register 0x11A = 0x00

CLKout6_7_PD 0

CLKout6_7_ODL 0

CLKout6_7_IDL 0

DCLK6_7_DDLY_PD 0

DCLK6_7_DDLY[9:8] 0

DCLK6_7_DIV[9:8] 0

Register 0x11B = 0x00

Reserved == 1 0

CLKout6_SRC_MUX 0 == Device Clock

DCLK6_7_PD 0

DCLK6_7_BYP 0

DCLK6_7_DCC 0

DCLK6_7_POL 0

DCLK6_7_HS 0

Register 0x11C = 0x34

CLKout7_SRC_MUX 1 == SYSREF

SCLK6_7_PD 1

SCLK6_7_DIS_MODE 1

SCLK6_7_POL 0

SCLK6_7_HS 0

Register 0x11D = 0x00

SCLK6_7_ADLY_EN 0

SCLK6_7_ADLY 0

Register 0x11E = 0x08

SCLK6_7_DDLY 8

Register 0x11F = 0x01

CLKout7_FMT 0

CLKout6_FMT 1

Register 0x120 = 0x01

DCLK8_9_DIV[7:0] 1

Register 0x121 = 0x00

DCLK8_9_DDLY[7:0] 0

Register 0x122 = 0x60

CLKout8_9_PD 0

CLKout8_9_ODL 1

CLKout8_9_IDL 1

DCLK8_9_DDLY_PD 0

DCLK8_9_DDLY[9:8] 0

DCLK8_9_DIV[9:8] 0

Register 0x123 = 0x00

Reserved == 1 0

CLKout8_SRC_MUX 0 == Device Clock

DCLK8_9_PD 0

DCLK8_9_BYP 0

DCLK8_9_DCC 0

DCLK8_9_POL 0

DCLK8_9_HS 0

Register 0x124 = 0x20

CLKout9_SRC_MUX 1 == SYSREF

SCLK8_9_PD 0

SCLK8_9_DIS_MODE 0

SCLK8_9_POL 0

SCLK8_9_HS 0

Register 0x125 = 0x00

SCLK8_9_ADLY_EN 0

SCLK8_9_ADLY 0

Register 0x126 = 0x08

SCLK8_9_DDLY 8

Register 0x127 = 0x44

CLKout9_FMT 4

CLKout8_FMT 4

Register 0x128 = 0x08

DCLK10_11_DIV[7:0] 8

Register 0x129 = 0x0A

DCLK10_11_DDLY[7:0] 10

Register 0x12A = 0x80

CLKout10_11_PD 1

CLKout10_11_ODL 0

CLKout10_11_IDL 0

DCLK10_11_DDLY_PD 0

DCLK10_11_DDLY[9:8] 0

DCLK10_11_DIV[9:8] 0

Register 0x12B = 0x50

Reserved == 1 1

CLKout10_SRC_MUX 0 == Device Clock

DCLK10_11_PD 1

DCLK10_11_BYP 0

DCLK10_11_DCC 0

DCLK10_11_POL 0

DCLK10_11_HS 0

Register 0x12C = 0x10

CLKout11_SRC_MUX 0 == Device Clock

SCLK10_11_PD 1

SCLK10_11_DIS_MODE 0

SCLK10_11_POL 0

SCLK10_11_HS 0

Register 0x12D = 0x00

SCLK10_11_ADLY_EN 0

SCLK10_11_ADLY 0

Register 0x12E = 0x01

SCLK10_11_DDLY 1

Register 0x12F = 0x00

CLKout11_FMT 0

CLKout10_FMT 0

Register 0x130 = 0x01

DCLK12_13_DIV[7:0] 1

Register 0x131 = 0x00

DCLK12_13_DDLY[7:0] 0

Register 0x132 = 0x60

CLKout12_13_PD 0

CLKout12_13_ODL 1

CLKout12_13_IDL 1

DCLK12_13_DDLY_PD 0

DCLK12_13_DDLY[9:8] 0

DCLK12_13_DIV[9:8] 0

Register 0x133 = 0x00

Reserved == 1 0

CLKout132_SRC_MUX 0 == Device Clock

DCLK12_13_PD 0

DCLK12_13_BYP 0

DCLK12_13_DCC 0

DCLK12_13_POL 0

DCLK12_13_HS 0

Register 0x134 = 0x20

CLKout13_SRC_MUX 1 == SYSREF

SCLK12_13_PD 0

SCLK12_13_DIS_MODE 0

SCLK12_13_POL 0

SCLK12_13_HS 0

Register 0x135 = 0x00

SCLK12_13_ADLY_EN 0

SCLK12_13_ADLY 0

Register 0x136 = 0x08

SCLK12_13_DDLY 8

Register 0x137 = 0x44

CLKout13_FMT 4

CLKout12_FMT 4

Register 0x138 = 0x18

VCO_MUX 0

OSCout_MUX 1

OSCout_FMT 8

Register 0x139 = 0x03

SYSREF_REQ_EN 0

SYNC_BYPASS 0

SYSREF_MUX 3 == SYSREF continuous

Register 0x13A = 0x03

SYSREF_DIV[12:8] 3

Register 0x13B = 0xE8

SYSREF_DIV[7:0] 232

Register 0x13C = 0x00

SYSREF_DDLY[12:8] 0

Register 0x13D = 0x08

SYSREF_DDLY[7:0] 8

Register 0x13E = 0x00

SYSREF_PULSE_CNT 0

Register 0x13F = 0x0D

PLL2_RCLK_MUX 0 == OSCin

PLL2_NCLK_MUX 0 == PLL2 Prescaler

PLL1_NCLK_MUX 1 == Feedback mux

FB_MUX 2 == SYSREF_DIV

FB_MUX_EN 1

Register 0x140 = 0x00

PLL1_PD 0

VCO_LDO_PD 0

VCO_PD 0

OSCin_PD 0

SYSREF_GBL_PD 0

SYSREF_PD 0

SYSREF_DDLY_PD 0

SYSREF_PLSR_PD 0

Register 0x141 = 0x80

DDLYd_SYSREF_EN 1

DDLYd12_EN 0

DDLYd10_EN 0

DDLYd8_EN 0

DDLYd6_EN 0

DDLYd4_EN 0

DDLYd2_EN 0

DDLYd0_EN 0

Register 0x142 = 0x00

DDLYd_STEP_CNT 0

Register 0x143 = 0x50

SYSREF_CLR 0

SYNC_1SHOT_EN 1

SYNC_POL 0

SYNC_EN 1

SYNC_PLL2_DLD 0

SYNC_PLL1_DLD 0

SYNC_MODE 0

Register 0x144 = 0xFF

SYNC_DISSYS_REF 1

SYNC_DIS12 1

SYNC_DIS10 1

SYNC_DIS8 1

SYNC_DIS6 1

SYNC_DIS4 1

SYNC_DIS2 1

SYNC_DIS0 1

Register 0x145 = 0x00

PLL1R_SYNC_EN 0

PLL1R_SYNC_SRC 0

PLL2R_SYNC_EN 0

Register 0x146 = 0x00

CLKin_SEL_PIN_EN 0

CLKin_SEL_PIN_POL 0

CLKin2_EN 0

CLKin1_EN 0

CLKin0_EN 0

CLKin2_TYPE 0

CLKin1_TYPE 0

CLKin0_TYPE 0

Register 0x147 = 0x1A

CLKin_SEL_AUTO_REVERT_EN 0

CLKin_SEL_AUTO_EN 0

CLKin_SEL_MANUAL 1

CLKin1_DEMUX 2

CLKin0_DEMUX 2

Register 0x148 = 0x0B

CLKin_SEL0_MUX 1

CLKin_SEL0_TYPE 3

Register 0x149 = 0x0B

SDIO_RDBK_TYPE 0

CLKin_SEL1_MUX 1

CLKin_SEL1_TYPE 3

Register 0x14A = 0x02

RESET_MUX 0

RESET_TYPE 2

Register 0x14B = 0x16

LOS_TIMEOUT 0

LOS_EN 0

TRACK_EN 1

HOLDOVER_FORCe 0

MAN_DAC_EN 1

MAN_DAC[9:8] 2

Register 0x14C = 0x00

MAN_DAC[7:0] 0

Register 0x14D = 0x00

DAC_TRIP_LOW 0

Register 0x14E = 0x00

DAC_CLK_MULT 0

DAC_TRIP_HIGH 0

Register 0x14F = 0x7F

DAC_CLKC_NTR 127

Register 0x150 = 0x09

CLKin_OVERRIDE 0

HOLDOVER_EXIT_MODE 0

HOLDOVER_PLL1_DET 0

LOS_EXTERNAL_INPUT 1

HOLDOVER_VTUNE_DET 0

CLKin_SWITCH_CP_TRI 0

HOLDOVER_EN 1

Register 0x151 = 0x02

HOLDOVER_DLD_CNT[13:8] 2

Register 0x152 = 0x00

HOLDOVER_DLD_CNT[7:0] 0

Register 0x153 = 0x00

CLKin0_R[13:8] 0

Register 0x154 = 0x04

CLKin0_R[7:0] 4

Register 0x155 = 0x00

CLKin1_R[13:8] 0

Register 0x156 = 0x04

CLKin1_R[7:0] 4

Register 0x157 = 0x00

CLKin2_R[13:8] 0

Register 0x158 = 0x96

CLKin2_R[7:0] 150

Register 0x159 = 0x00

PLL1_N[13:8] 0

Register 0x15A = 0x01

PLL1_N[7:0] 1

Register 0x15B = 0x14

PLL1_WND_SIZE 0

PLL1_CP_TRI 0

PLL1_CP_POL 1

PLL1_CP_GAIN 4

Register 0x15C = 0x3F

PLL1_DLD_CNT[13:8] 63

Register 0x15D = 0xFF

PLL1_DLD_CNT[7:0] 255

Register 0x15E = 0x1E

HOLDOVER_EXIT_NADJ 30

Register 0x15F = 0x3B

PLL1_LD_MUX 7

PLL1_LD_TYPE 3

Register 0x160 = 0x00

PLL2_R[11:8] 0

Register 0x161 = 0x01

PLL2_R[7:0] 1

Register 0x162 = 0xA4

PLL2_P 5

OSCin_FREQ 1 == 63 to 127 MHz

PLL2_XTAL_EN 0

PLL2_REF_2X_EN 0 == Doubler disabled

Register 0x163 = 0x00

PLL2_N_CAL[17:16] 0

Register 0x164 = 0x00

PLL2_N_CAL[15:8] 0

Register 0x165 = 0x05

PLL2_N_CAL[7:0] 5

Register 0x166 = 0x00

PLL2_N[17:16] 0

Register 0x167 = 0x00

PLL2_N[15:8] 0

Register 0x168 = 0x05

PLL2_N[7:0] 5

Register 0x169 = 0x59

PLL2_WND_SIZE 2

PLL2_CP_GAIN 3

PLL2_CP_POL 0

PLL2_CP_TRI 0

PLL2_DLD_EN 1

Register 0x16A = 0x3F

PLL2_DLD_CNT[13:8] 63

Register 0x16B = 0xFF

PLL2_DLD_CNT[7:0] 255

Register 0x16E = 0x06

PLL2_LD_MUX 0

PLL2_LD_TYPE 6

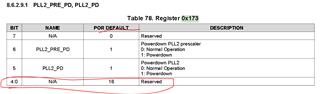

Register 0x173 = 0x0F

PLL2_PRE_PD 0

PLL2_PD 0

Register 0x177 = 0x00

PLL1R_RST 0

Register 0x182 = 0x00

CLR_PLL1_LD_LOST 0

CLR_PLL2_LD_LOST 0

Register 0x183 = 0x05

RB_PLL1_DLD_LOST 0

RB_PLL1_DLD 1

RB_PLL2_DLD_LOST 0

RB_PLL2_DLD 1

Register 0x184 = 0x50

RB_DAC_VALUE[9:8] 1

RB_CLKin2_SEL 0

RB_CLKin1_SEL 1

RB_CLKin0_SEL 0

RB_CLKin2_LOS 0

RB_CLKin1_LOS 0

RB_CLKin0_LOS 0

Register 0x185 = 0xAF

RB_DAC_VALUE[7:0] 2

Register 0x188 = 0x41

RB_HOLDOVER 0

RB_DAC_RAIL 0

RB_DAC_HIGH 0

RB_DAC_LOW 0

RB_DAC_LOCKED 1