Hi team,

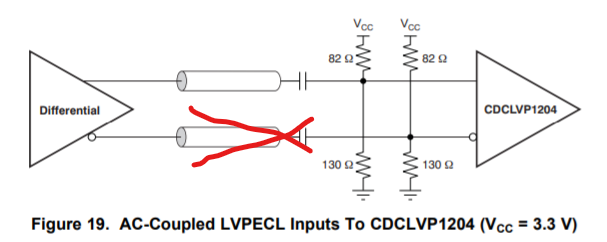

My customer is planning to use a 200MHz LVPECL clock. For the configuration below, they want to drive the CDCLVP1204 single-ended with a square-wave. What is the recommended minimum voltage? I see recommended specs for differential but not single-ended.

Thanks,

Connie