Other Parts Discussed in Thread: LMX2430

Hi team,

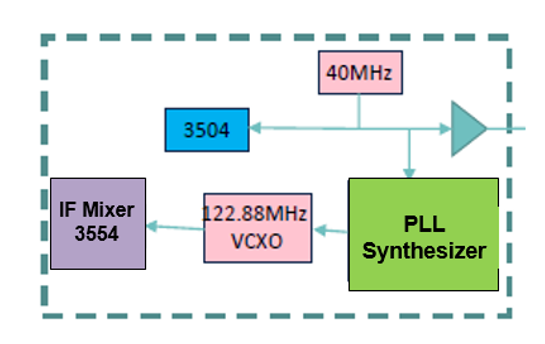

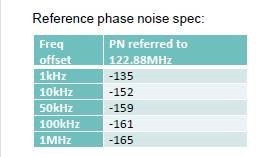

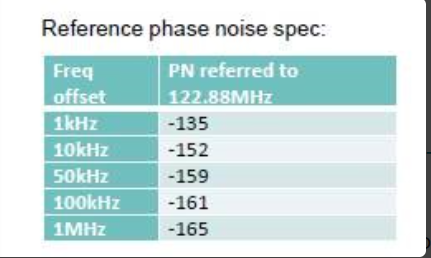

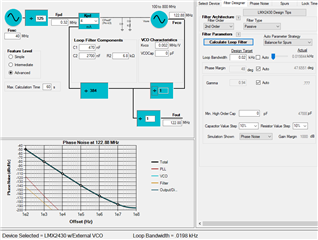

My customer is looking for a PLL synthesizer. The phase noise spec and block diagram is as below figure.

Originally, they used ADF4002 and ADF4150 for old design. But, it looks total phase noise will be limited to

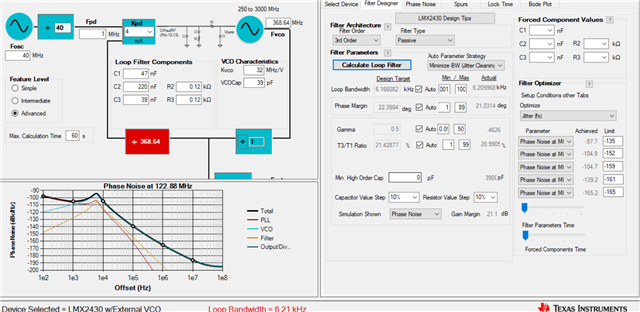

ADF4002’s PN performance. ADF4150’s Chip PN is better than ADF4002 at 122.88MHz. VCO RFin should be set to 983.04Mhz based on programmable divide design by 1/2/4/8/16 output. According to simulate results, it looks total phase noise will be limited to VCXO PN performance as table shown the phase noise and jitter data . I have searched our solution and propose our LMX2571. Do we have more suitable solution for their design from spec and cost perspective? Thanks.