Part Number: SE555

Hello,

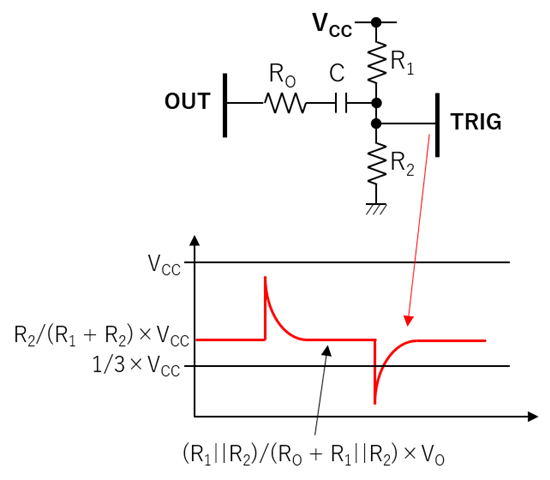

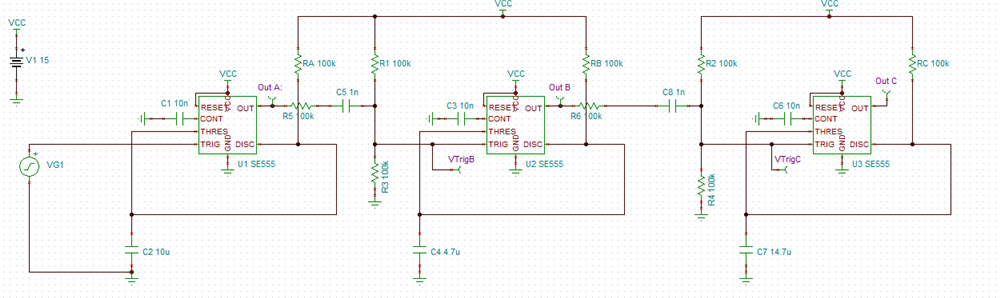

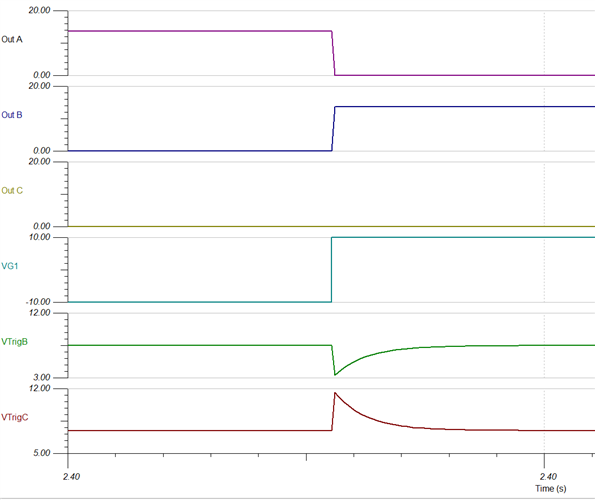

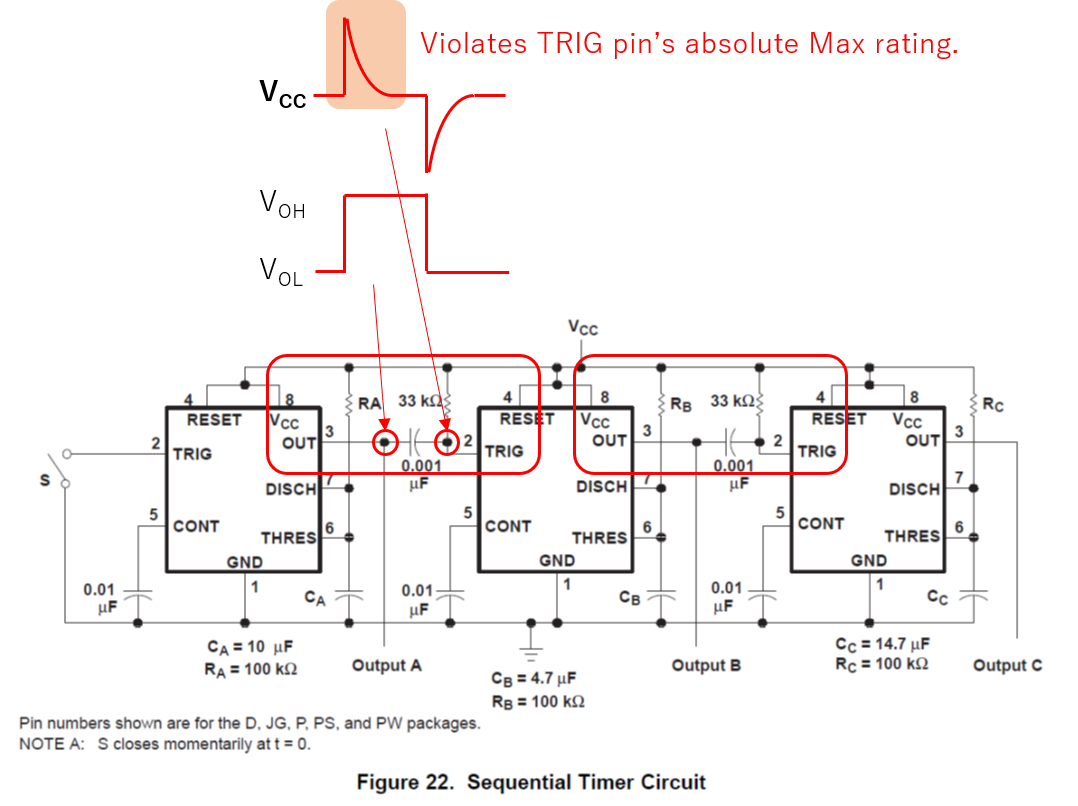

I've noticed SE555's sequential timer circuit in Figure 22 of its data sheet violates its TRIG pin's absolute Max rating. Do you agree with me? The TRIG pin's absolute Max rating is defined as VCC (Max), but the pin's waveform after an RC circuit exceeds the VCC when an OUT pin voltage of the previous stage rises.

Do you have any workaround for this?

Best regards,

Shinichi Yokota