Other Parts Discussed in Thread: LMK04832

Hi,

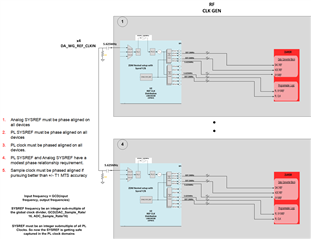

We want to use LMK04828 CLK synthesizer for RFSoC FPGA for multi-board synchronization (ADC/DAC sampling)

Below are the specs

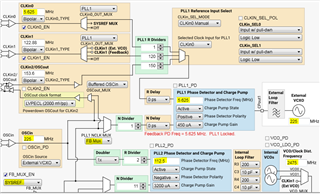

1] ADC sampling rate = 1350Mhz

2] DAC sampling rate = 5400MHz

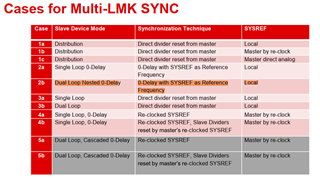

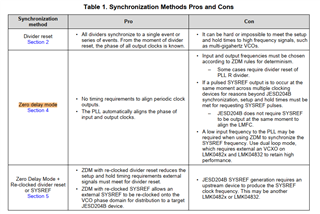

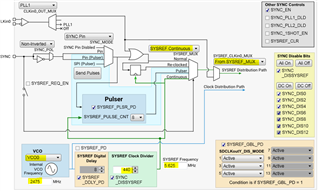

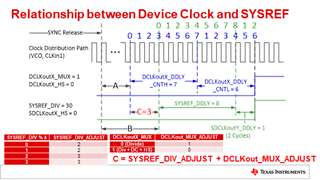

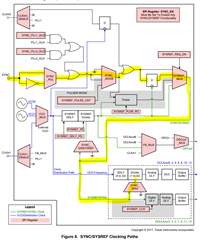

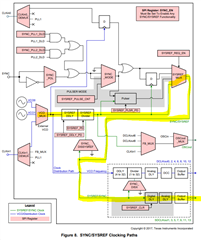

We are following "Synchronization Method: ZDM" with the below rules

So please verify my clock scheme for multi-board SYNC

Keeping into rules in account

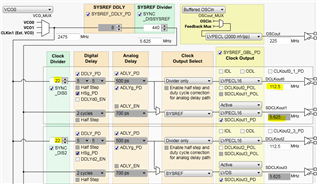

ADC/DAC CLK = 337.5MHz

SYSREF = 5.625MHz

I/P REF FREQ = 5.6225MHz

Please validate the same