- Ask a related questionWhat is a related question?A related question is a question created from another question. When the related question is created, it will be automatically linked to the original question.

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

Hi team,

We got inquires from customer as following.

Thank you and best regards,

Michiaki

Hello Michiaki,

1. The ADS1672 will meet full datasheet performance with CLK duty cycle from 45% to 55%.

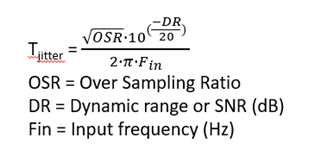

2. Maximum clock jitter can be calculated using the following equation:

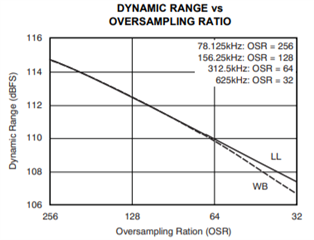

With data rate set to 625ksps, OSR=32. The dynamic range at OSR=32 for the ADC is 107.5dB. This is the internal thermal noise limit of the ADC. Clock jitter will add additional noise. In order to limit this additional noise to a small percentage of the thermal noise, we will set the DR limit for the jitter calculation to be 107.5+10dB, or 117.5dB. Per above requirements, the maximum input frequency will be 60kHz.

OSR=32

DR=117.5dB

Fin=60kHz

T-jitter = [sqrt(32)*10^(-117.5/20)]/[2*3.14*60000] = 20ps

Regards,

Keith Nicholas

Precision ADC Applications