Hi all,

I'm using ADS1282-SP for the first time and I have to design the FPGA which controls it. Being the latter an OTP device I have no room for errors.

My intention is to use the ADS1282-SP ADC in Read Data Continuous (RDATAC) mode and in pulse-sync mode.

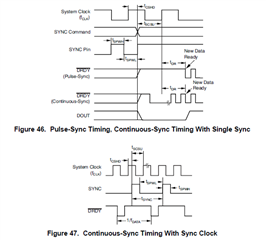

The datasheet reports two figures to compare pulse-sync with continuous-sync reading modes.

In continuous-syncmode is possible to use a clock-like pulse signal respecting all the constraints w.r.t. the ADC Clock. and it's very clear.

What I need to understand clearly is the form the SYNC pulse shall have when working in Pulse-Sync mode.

Shall ADC's SYNC input be driven high then low and then high again (w.r.t. timing constrains) or shall it be driven low-to-high only once to trigger a new conversion?

Shall SYNC pin stay high for all the time I am reading data and be driven low only when I don't need to read converted data output by the ADC? in other words, does SYNC pin have effect on enabling/disabling /DRDY output?

Waiting for your kind reply.

Best regards,

Daniele Lippi