Hi All,

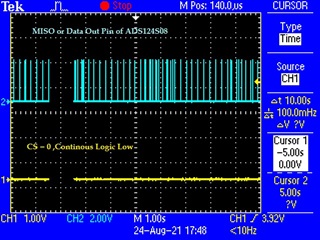

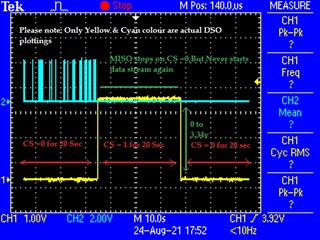

We are using ADS124S08 IC in one of our project. We are facing some communication issues with Chip Select (CS) pin. When we directly connect the CS pin to DGND (means we have connected CS pin to DGND using external jumpers) the IC works fine and we able to read all the 12 channels (single ended) properly.

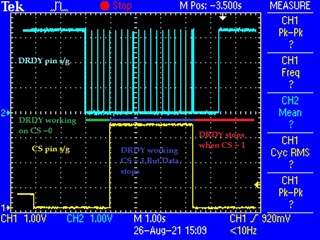

We are using Raspberry PI compute module (CM-4) to communicate with ADS124S08. And when we tied CS pin (of ADC) to CM-4 Chip select pin we are not getting proper reading (it showing garbage values of 0-2mV) where the actual Input signal on AIN pins was 0.5V-2V.Gain is set to 1.

In our project we have used two ADS124S08, if we forced ground first ADC IC using Jumper J1=closed & J2=open (schematic attached) the First IC works fine but the other one gets inactive and vice versa. Our Aim is to get the readings from both the ADC ICs and It will be possible only if we able to control/toggle CS pin of both from GPIO pins (not by physical ground).

While getting garbage data, we even tried giving Reset to ADC (by connecting RESET pin to ground ) but we still getting wrong data. Until we power reboot the entire device (with CS pin connected to ground).

Things we tried are as follows.

a. We check our signal on CS pins on Digital Oscilloscope, when its LOW it is giving proper 0V and on HIGH it is 3.3V.

b. We tried giving CS signals from other available GPIO pins on CM-4 module.

c. Connect Pull down resistor 10k & 4.7K (one at a time) to CS pin.

d. Tried controlling CS pin using NPN transistor (BC847).

Are we missing any register reading/writing, Reading sequence, Timing, or any hardware point etc.

Please suggest. Thanks in advance