Other Parts Discussed in Thread: OPA2189, ADS1235, ADS1261

Hello, do you have an app note about driving the input stage on the ADS1255? There is not really sufficient information in the datasheet. It doesn't even specify the acquisition time as far as I can see.

For example, please see page 23 of this A/D converter. This description is pretty comprehensive.

https://www.analog.com/media/en/technical-documentation/data-sheets/2400fa.pdf

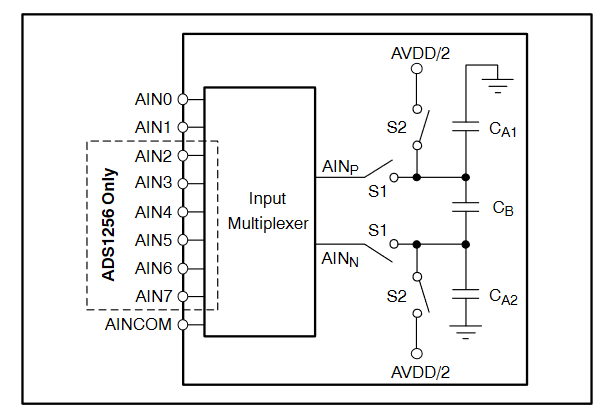

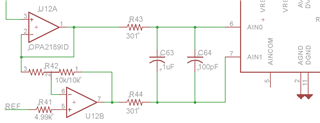

The ADS1255 shows an example of using 300 ohms and .1uF on the input (Figure 25) but makes absolutely no reference to how this effects settling time, etc. Also, it makes no mention of how fast the amplifier needs to be that is driving it.