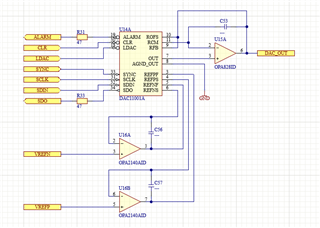

Other Parts Discussed in Thread: OPA828, , DAC11001B

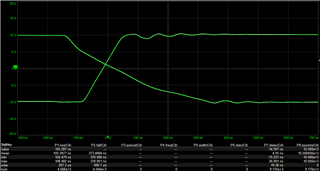

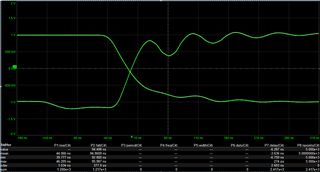

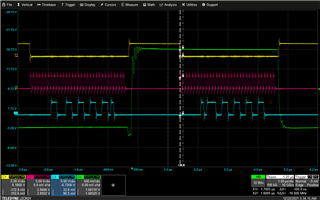

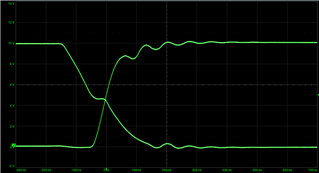

The slew rate seems to be dependent on slope direction, see screenshot. This is the DACs output buffered with an OPA828 (and another line driver). The initialization parameters are 0x02000200 and 0x06000080, after this 0x01FFFFF0 and 0x01000000 are repeatedly sent to the DAC to generate a full scale rectangular waveform. I tried also some other settings but that didn't help. What is the reason for this asymmetric behavior?