Other Parts Discussed in Thread: CDCE62005, DAC3482, DAC3484

Hello!

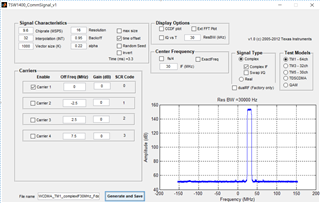

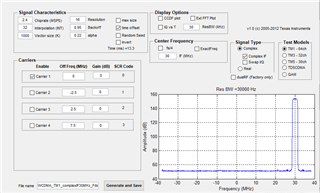

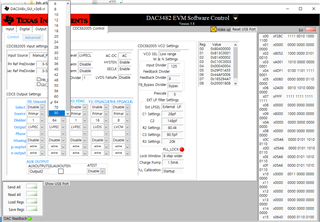

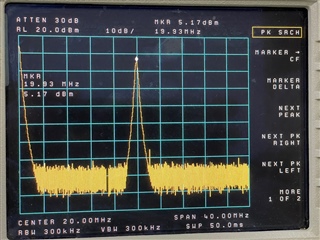

I need the pattern file to be used in TSW1400EVM.

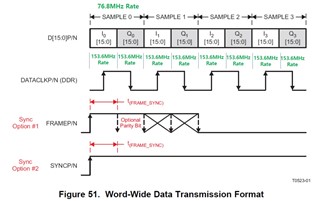

There is WCDMA_TM1_complexIF30MHz_Fdata307.2MHz_1000.tsw as the provided pattern file, but WCDMA_TM1_complexIF30MHz_Fdata76.8MHz_1000.tsw with Fdata changed to 76.8MHz is required.

thank you.