TI JESD204C IP was placed on xilinx ultra scale and connected to ADS42jb49.

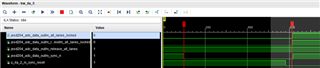

According to the TI JESD20T IP document, the master_reset and sync_reset signals have been raised and lowered.

And it was confirmed that the data was transferred from the ADC to the FPGA.

It was confirmed that lane lock, rx data valid signal is displayed as 1.

The K and F values of jesd of adc and jesd of fpga were set, and scramble was not performed.

The lmfc clock seems to be right in my opinion.

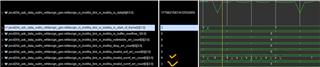

And when I set the ADC to output the data filled with 1s, and looking at the data received from the FPGA, most of them are 1s, but sometimes 0s are inserted.

And it was confirmed that the eomf error count was increased.

What part of the setting was not made?