Other Parts Discussed in Thread: ADS4245

Hi,

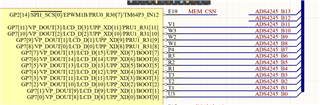

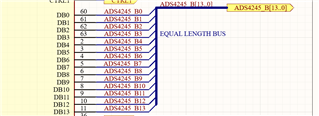

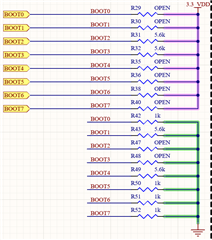

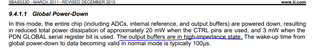

Does pulling CTRL1 high and CTRL2/3 low configure ADS4245 to global power down? Do I need to write to registers to achieve this?

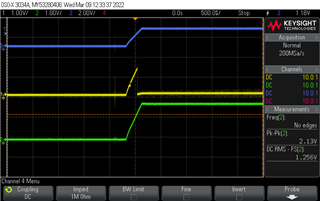

Also, what is the state of output during global power down?

The issue is we configured the CTRL pins for global power down and it does not work as we do not see hi-z state on outputs. Please assist.

Thanks,

Pawan