Other Parts Discussed in Thread: TPS22810

This is an issue that came up a few years ago, where the DRDY was not asserted due to the Internal Clock not starting properly:

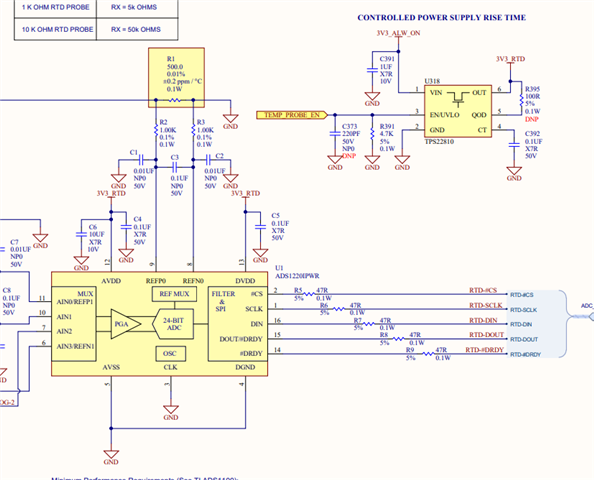

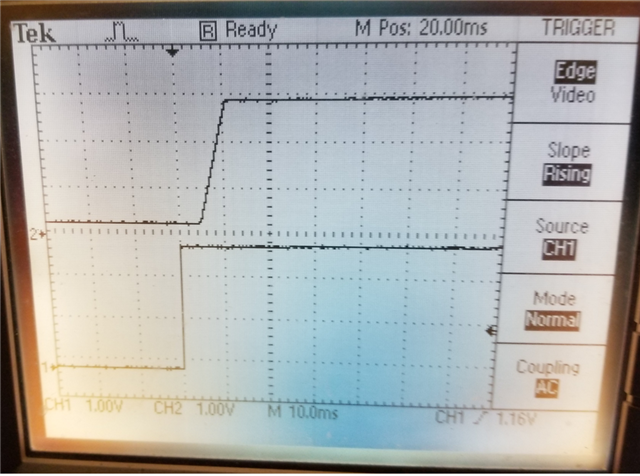

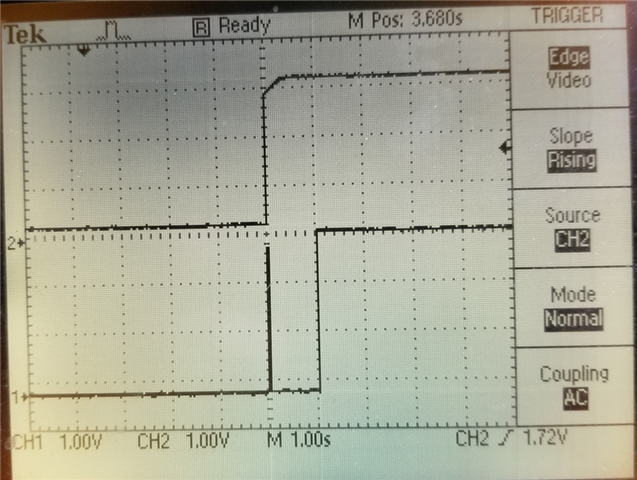

The recommended solution is to implement a Controlled Rise Time on the A2D power supply. We implemented a special Rise Time Controlled Switch, and the number of problem occurrences appeared to be significantly reduced. Due to the Pandemic, we did not visit our Contract Manufacturer. Not all customers use the A2D (for Temperature Measurement). Recently, we did find our CM was having problems, and Field Problems were being reported.

Our product switches on the Controlled Rise Time Power to the A2D, and then after a delay, checks that the DRDY is asserted (POR on A2D causes a one time conversion). If we do not see the DRDY asserted, we deem this a failure. Knowing that an external event such as a single clock on the SPI CLK will clear the asserted DRDY, I would ask if there is another method to confirm the A2D is actually properly operating (with internal clock operating normally). Most of our Field Returns are due to this issue!!

Thank You,

Paul Masanek

Liquid Controls