Hello,

I would like you to confirm about below.

* According to schematic of EVM, REFBUF voltage come from AVDD via J16(Jamper 16).

However, it seems that input timing to AVDD pin and REFBUF pin is same.

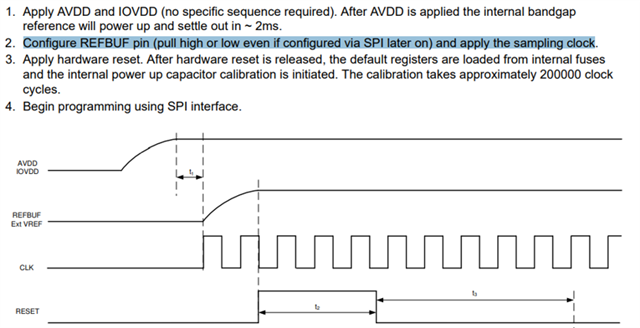

According to datasheet 10 Initialization Set Up, TI described that min time b/w AVDD and REFBUF is 2ms.

So, it seems that EVM power up sequence is viorate this regulation.

Which one EVM setting and datasheet description is correct ?

BR,

-

Ask a related question

What is a related question?A related question is a question created from another question. When the related question is created, it will be automatically linked to the original question.