Other Parts Discussed in Thread: DAC5688

Dear TI,

We are currently using DAC5687-EP on one of our Software Defined Radio Design and we encountered some trouble with the DAC5687-EP.

It seems that we have spurs with a frequency equals to fs/4 at the output of the DAC. We are using the DAC in NCO mode and set the sine frequency from 36.08MHz to 56.08MHz using a constant at the data input of the DAC.

The DAC input clocks are set to 192.86MHz in dual clock mode (CLK1 generated by an FPGA and CLK2 generated by clock source). We make a sweep of the DAC output frequency from 156.78MHz (192.86 - 36.08MHz) to 136.78MHz (192.86 - 56.08MHz).

The DAC registers are set to:

VERSION: 0x03

CONFIG_0: 0x02

CONFIG_1: 0x32

CONFIG_2: 0xc0

CONFIG_3: 0x80

SYNC_CNTL: 0xe0

SER_DATA_0: 0x00

SER_DATA_1: 0x00

NCO_FREQ_0: 0x55

NCO_FREQ_1: 0x55

NCO_FREQ_2: 0x35

NCO_FREQ_3: 0x3a

NCO_PHASE_0: 0x00

NCO_PHASE_1: 0x00

DACA_OFFSET_0: 0x00

DACB_OFFSET_0: 0x00

DACA_OFFSET_1: 0x00

DACB_OFFSET_1: 0x00

QMCA_GAIN_0: 0x00

QMCB_GAIN_0: 0x00

QMC_PHASE_0: 0x00

QMC_PHASE_GAIN_1: 0x00

DACA_GAIN_0: 0x00

DACB_GAIN_0: 0x00

DACA_DACB_GAIN_1: 0xff

DAC_TEST: 0x00

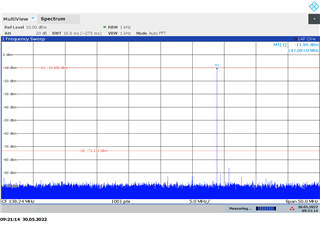

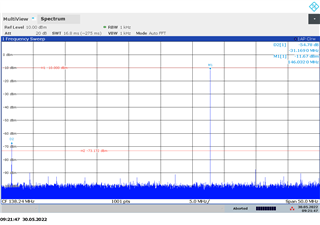

At 147.081MHz (span 50Mhz): The spur is not visible

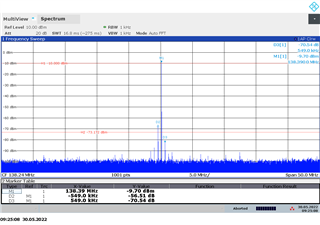

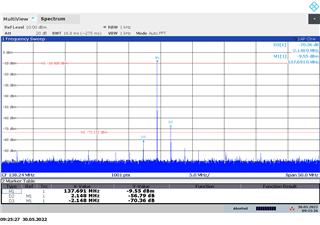

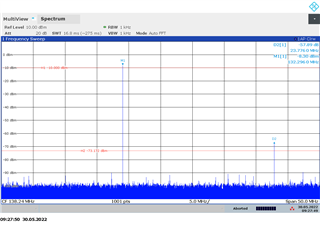

At 146.032MHz (span 50MHz): The spur is visible at 131.863Mhz

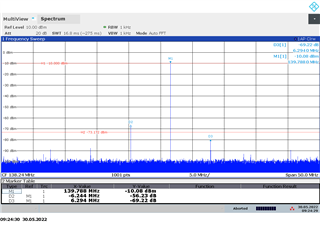

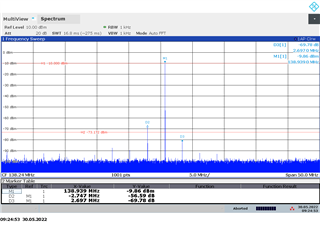

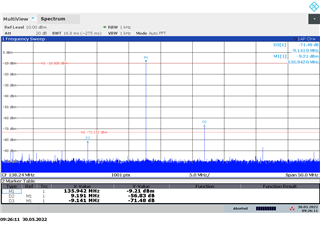

At 139.788MHz (span 50MHz): The spur and its mirror are seen (at : 133.544MHz and 146.082MHz)

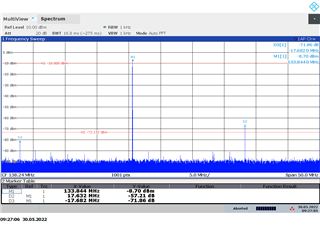

When we continue the sweep: we saw that the spur get closer to the output frequency of the DAC and then it go in the other direction when the frequency is crossed

The spurs level are too high for our application ( >60dBc) and we cannot explain this behaviour of the DAC as it is out of the characteristics explain in the datasheet.

Can you explain this spurs or are we using the DAC in a bad configuration ?

Regards,

Kévin