Hi team,

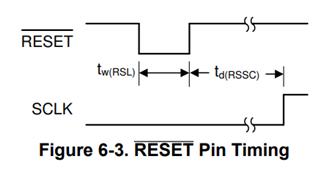

I got question about RESET / SCLK timing for td(RSSC).

As shown in Figure 6-3 in D/S, do we need to keep SCLK "Low" while td(RSSC) timing?

Or td(RSSC) is just a time that the communication has not started, thus we can input the SCLK without any problems?

Best regards,

Yuto