HI.

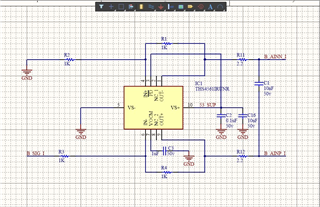

I am trying to do SPI communication with my ADS8900 custom board, my strategy is as follows.

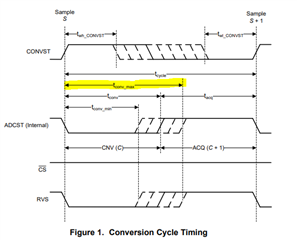

1. with rising edge of sampling clock. CONVST pin is pulled low.

2. Host controller/ FPGA moniotrs the RVS pin for a rising edge.

3. With the rising edge on RVS pin host contrller pulls low the CS line and provide 22 serial clock to th ADS8900 sclk pin.

(basically fig 47 zone 1 data transfer)

1. My question is what should i actually send through the SDO pin (like can i send 0x67A89) to collect the 20 bit sample in SDI3 pin of the ADS8900 ? some data is given in data sheet (page no 27) but i am not clear with my understaning.

2. Can I power 6 ADS8900B with a single TPS7A4700 IC ?

regards

-----------

Pratik