Hello team,

I have two quick questions for DAC3482. Could you please confirm below?

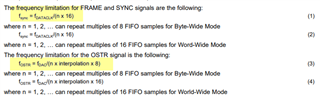

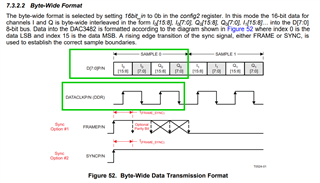

- Datasheet equation 1 on p.32 is all same as equation 2. Is equation 1 correct? not "fsync = fdataclk / (n x 8)"?

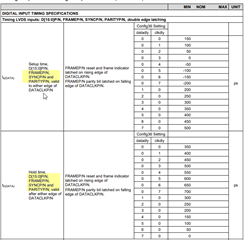

- SYNCP/N is captured with rising edge of DATACLKP/N, similar to FRAMEP/N? or falling edge or DATACLKP/N?

Best regards,