Other Parts Discussed in Thread: LMK04828, LMX2594

Hi team,

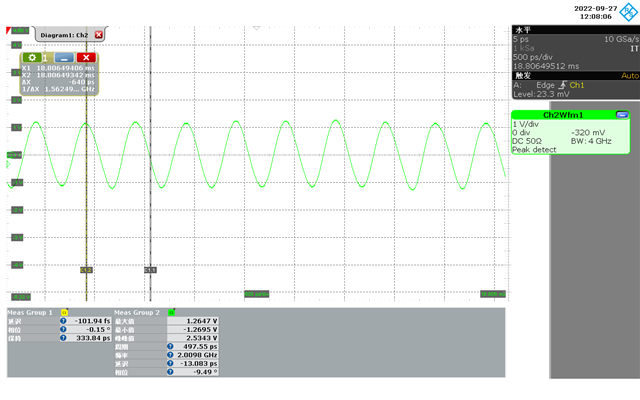

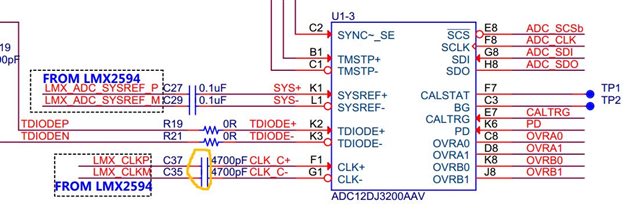

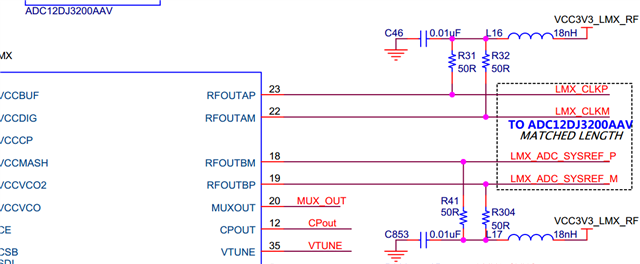

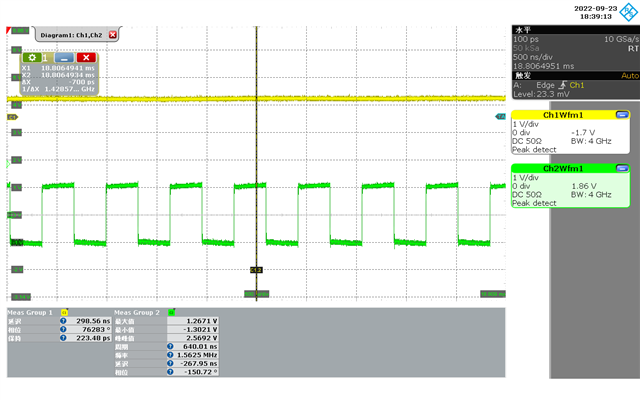

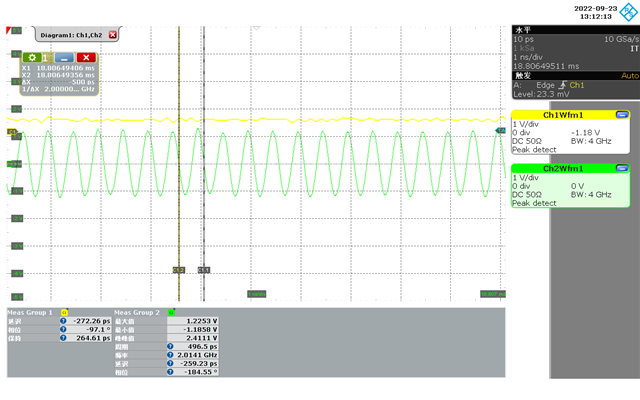

The customer uses their own design board, the FPGA is 420T, the refclk and the reference clock of the FPGA is generated by LMK04828, the LMK connects the LMX2594 to output the ADC device clock and the reference clock. The oscilloscope can observe the generated clock signal.

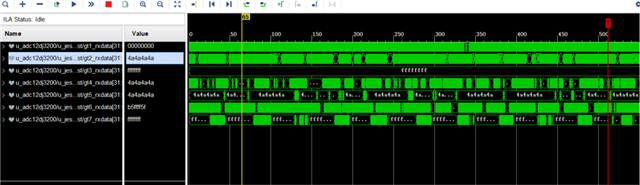

JMODE1,ILA observed sync signal is pulled low but xillnx IP core tdata has no data input (K28.5), and the foreground calibration on the ADC could not be completed, 0x6A always reads 0C.

This is the signal captured by the ILA

Best Regards