Other Parts Discussed in Thread: DAC37J82, , LMK04828

Hi!

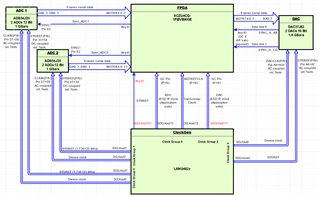

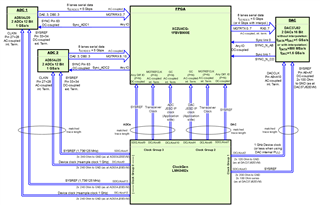

We have a new project where we want to connect two ADCs and a DAC via JESD204B with a Xilinx Ultrascale+ XCZU4CG.

I read several information about JESD204B already, but I have still some questions especially about connecting clocks from LMK0482x to FPGA.

Our plan so far:

- MPSoC XCZU4CG-1FBVB900E

- LMK0482x PLL / clock cleaner

- 2 x ADS54J20 devices (4 ADCs)

- ADC LMFS configuration 8224. So 8 lanes at 5 Gbps per ADS54J20 device (16 lanes in total).

- 1 x DAC37J82 (2 DACs)

- JESD204B subclass 1

My questions:

- Do we have to connect the "device clock" to MGTREFCLKxP/N or to FPGA clock pins (GC, QBC)?

- I read that SYSREF must be connected to FPGA clock pins. But to which clock pins? Do they have special requirements like GC or QBC clock pins at a HP bank or would HDGC clock pins on a HD bank be fine?

- Does SYNC need a general I/O on HP bank or would any pin on a HD bank be fine? Should it be located in the same bank as the SYSREF clock?

Best regards,