- Ask a related questionWhat is a related question?A related question is a question created from another question. When the related question is created, it will be automatically linked to the original question.

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

Hi team,

There is application that ADC122S021 is used with /CS pin low for continuous conversion, but can customer use /CS pin to reset ADC, i.e. to toggle /CS pin to start a fresh conversion?

If no, is there any other method to reset ADC122S021 (without power reset)?

If yes, how long is needed to pull /CS pin high to reset the ADC?

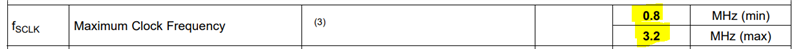

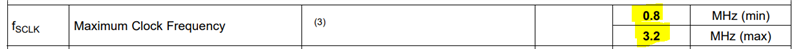

One more question, is effective sample rate always 1/16 of fsclk due to throughput is 16 SCLK cycles?

Hi Py,

I am hesitant to use the word 'reset' without fully knowing the context of your query. If the intention is to re-start a conversion or re-synchronize SDI to SDO, then yes, raising /CS would accomplish that. The minimum high time would be one SCLK period. If the ADC122S021 is 'stuck' and not responding to SDI at all, it may require a power cycle to recover.

Hi Tom,

Thank you. Do you see any problem/issue with ADC122S021 used with /CS pin always low? Datasheet has stated such usage, i.e. continuous conversion.

One more question, is effective sample rate always 1/16 of fsclk due to throughput is 16 SCLK cycles?

Hi PY,

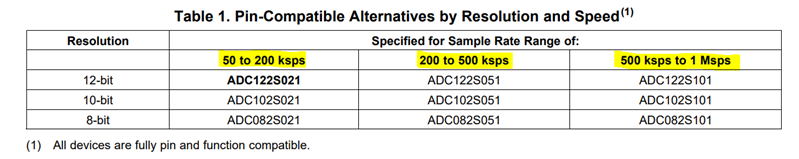

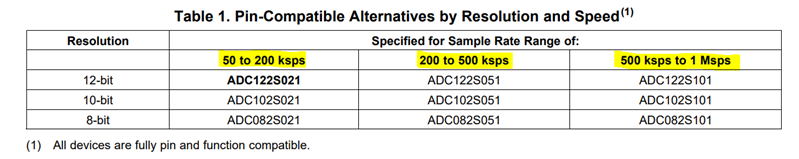

There is no issue with leaving /CS low. Yes, the sample rates shown in Table 1 are all based on fSCLK/16 (MAX), which assumes the /CS is held low and the SCLK is continuous.