Other Parts Discussed in Thread: ADS8860

Hi,

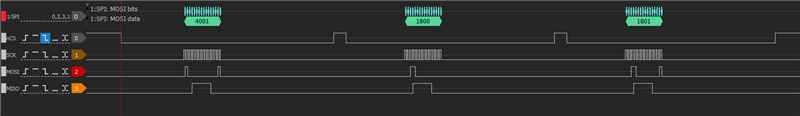

I have used the above part and was successfully written/read using 16-bit transfer mode. However, when I tried to do the same with 8-bit transfer mode, it doesn't seem to work. The only difference between the two modes is that I have about 7.6uS gap between two 8-bit clock cycles. The CS remains low during the entire two 8-bit cycles. The MOSI data is valid as well.

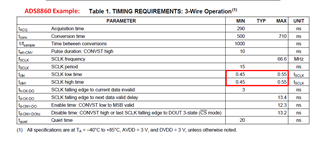

Following is the 16-bit cycles, which work. (All three cycles shown)

This is the first 8-bit cycle

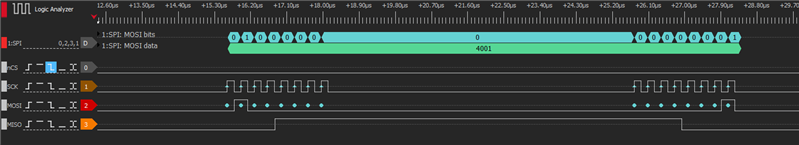

As far as SPI is concerned, both should be valid. I couldn't find any timing parameter from the ADS7960 data sheet, which could explain this. As far as I can see, we are having a long setup time between 8th and 9th clock cycles.

Any ideas?

Cheers,

Kaushalya