Other Parts Discussed in Thread: DAC8760EVM, DAC8760

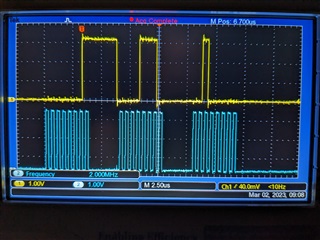

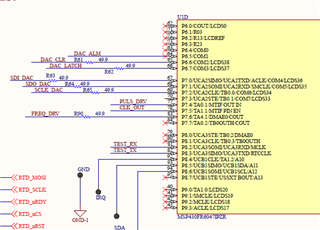

Our DAC7760 is sometimes reading an extra zero bit between the address byte and the first data byte. It doesn't happen all the time, but when it does, the problem will persist until a power cycle or perhaps a reset. I don't know yet what causes it or how to reliably avoid it. Here are three consecutive logic analyzer traces.

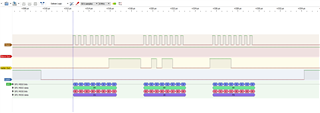

- Write DATA register with value 0x2CF0

- Write read command for DATA register

- Read DATA register as 0x1670 which is 0x2CF0 shifted one bit to the right

I have lots of traces like this. It's also not limited to the DATA register. I first saw the problem with the GAIN and ZERO registers. I'm running the SPI clock at 2MHz. I've verified the logic analyzer traces on a scope.

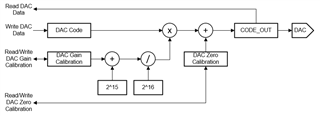

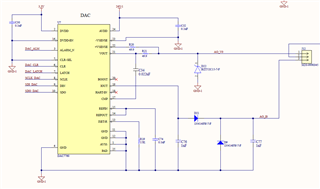

Our schematic:

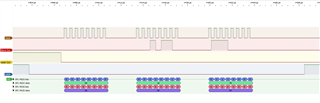

A write to DATA of 0E20. It was read back as 0710.