Hi team,

My customer has a question regarding the full-clock mode of ADS8683.

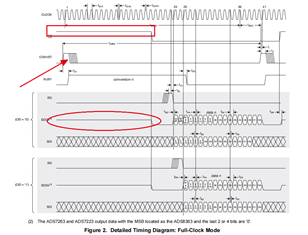

When the IC /CS signal is enabled, there is a rising edge of CONVST, but SDI and RD seem to be ignored and take no action according to the pin function, and SDO is a tri-state, so they want to know what is the exact function of SDI, RD and SDO this in this mode? (Looking at the timing diagram, the difference between the full clock mode and the half clock mode is mainly concentrated here). So they want to know the mainly difference between full-clock mode and half-clock mode.

Regards,

Xiaoying