Hello,

We have integrated 2 ADS131M06 with AM243x device.

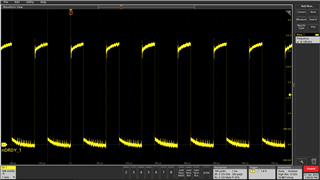

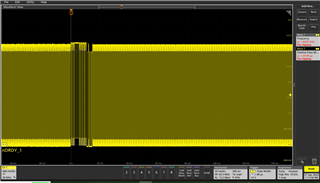

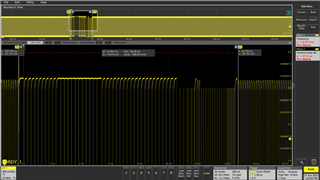

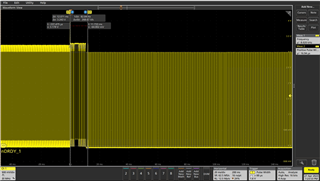

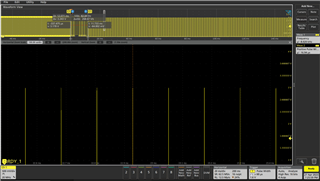

We are trying to reset the ADS131M06 devices by issuing a RESET command, when ADC s go out of sync.

We are however not able to get the ADC back to reading correct values even after initiating the RESET command.

-> Is there a timing requirement on when the RESET command can be given?

Thank you,

Prithvi