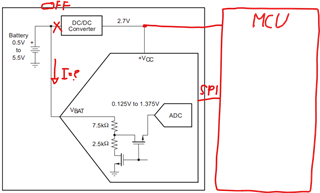

What is the battery drain current flow into VBAT pin in case of unpowered TSC2046 IC?

I think to situation, when VBAT pin is connected to battery, but there is a power switch between battery and DC/DC converter and is switched off.

Reference:

Low Voltage I/O Touch Screen Controller datasheet (Rev. G) (ti.com)