Hi team,

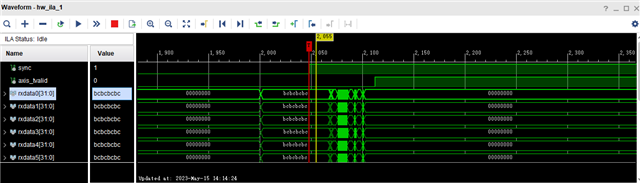

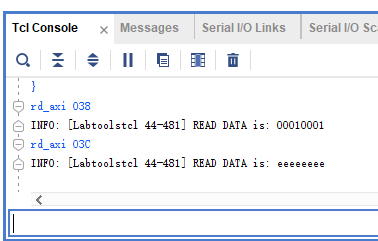

1) The ADS54J60 is configured to capture data and establish an 8224 link with JESD204B, strictly in the order of ADC hardware reset, SPI write, and JESD204B core reset. The link establishment should have been completed with the waveform data captured by the ILA (Online Logic Analyzer). And both the JESD status indication registers 0x038 and 0x03C indicate that synchronization and link establishment are complete (outputs 0x00010001 and 0xeeeeee, respectively). However, after the ADC sends K28.5 and ILA data, the valid data transmitted is 0.

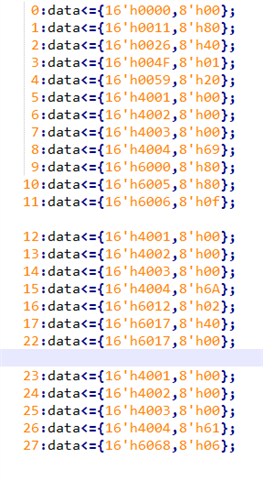

2) After writing to the 0x68h register on page 6100, the readback does not work correctly and the readback data is always 0. The remaining registers on the 6100 page, 6A00 page (whether they are read-write or not) have this problem, but the 6900 page registers with the same read-write timing can read back the written data normally. This might be the case of the above issue.

In addition, the customer confirms that they have switched to the corresponding page before each read back. The register write sequence is shown in the figure below. Each address switch waits 32 ms and PLL reset waits 160 ms:

Could you help check this case? Thanks.

Best Regards,

Cherry