Hi,

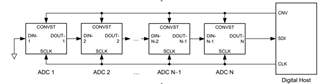

We use 4 pcs. Of ADS8864 in daisy chain connection without busy indicator as described in the datasheet:

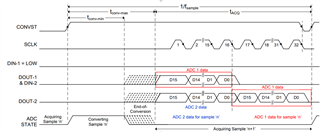

In datasheet it is stated:

A total of 16 x N SCLK falling edges are required to capture the outputs of all N devices in the chain. Data can be read at either SCLK falling or rising edges.

However, when using 15 MHz SPI clock it seems that (16 x N)+ 1 SCLK falling edges are needed. It seems that the first falling edge doesn’t shift out the measured data, but the second does. Busy indicator is not used. The reading is done on rising edge of SCLK due to better stability.

Additional clock cycle is done using extra byte reading and left-shifting read data. But when I change the SPI clock frequency to 30 MHz (screenshot below) 1 extra SCLK falling edge seem to be not enough. Now the data are stable only when using that (16 x N) + 2 SCLK falling edges.

I cannot understand the behaviour. I tried to extend the delay between rising edge of CONVST signal and start of SCLK (from 1.5us to 3.1us), but there is no difference in the behaviour. Can you please explain the reason for this behaviour? I was able to get stable data, but I would like to understand the behaviour of the IC, in order to prevent unexpected outputs in the feature.

thanks