Other Parts Discussed in Thread: SN74LVC8T245

Hi there

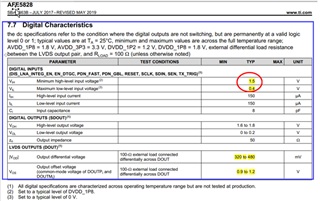

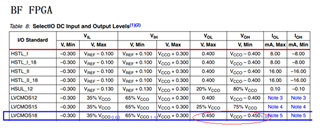

we are designing FPGA to control AFE5828, here is a concern about IO standard Voltage level compatible. FPGA IO output pins are LVCMOS1V8 (JESD 8C.01 ) standard, directly connect to AFE's 1.8V-logic inputs (like reset, PDN_GBL, .....and SEN, SCLK, SDIN ...etc)。

Below is the voltage level of AFE and FPGA, as I cycled out, there seems RISK that FPGA's VoL(max 0.45V) > AFE's ViL(max 0.4V), and FPGA's VoH(min 1.35V) < AFE's ViH(min 1.5V). which means that AFE may not receive correct logic inputs under some boundary conditions. How do you think?

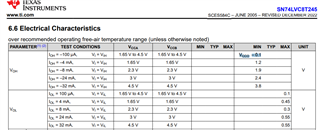

One possible solution is to insert a logic buffer (1.8V to 1.8V) ,such as TI SN74LVC8T245. However, its VoL and VoH is dependent on load current(as below pic).

So, how could we estimate the load current based on AFE's 1.8V-logic input s parameters, especially on AFE's SPI inputs ( SPI works on 20MHZ frequency)?

By the way, does AFE5828's 1.8V-logic inputs / outputs compliant to JESD LVCMOS1V8 standard?

Thanks a lot.