Other Parts Discussed in Thread: LMK04828, ,

Dear TI experts,

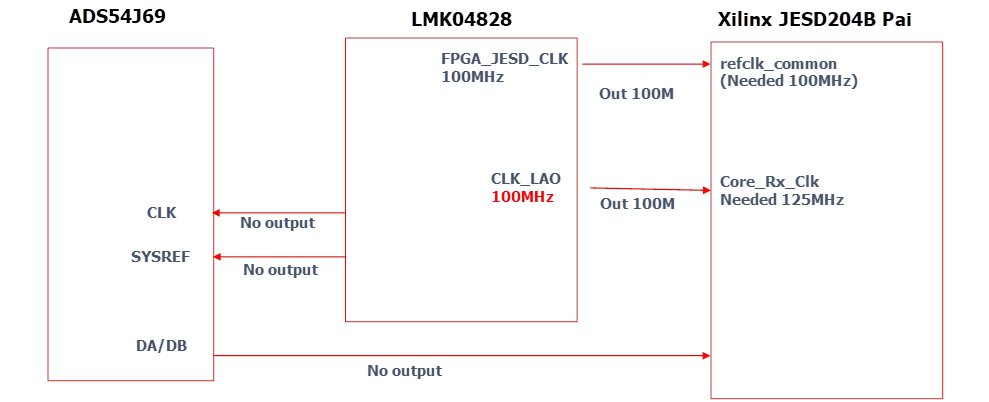

My customer now tests ADS54J69 with LMK04828 and xilinx FPGA (use JESD204B)

the block diagram is as below;

They confirmed FPGA_JESD_CLK as 100MHz. (it is okay)

and changed Clkout 12 and 13 DCLK Divider from 30 to 24 -> confirmed 125MHz output. (is it right to fix this configuration?)

the problem is they could not see the output from DCLKOUT2 and SDCLKOUT3 of LMK04828.

attached file is the configuration of GUI. Could you check the settings and find right configurations for these outputs?

Please let me know if you need more information about it. Thanks.

Best regards,

Chase