ADC team,

Our customer is using ADC082S021 and seeing digital results that are twice the expected value, but only on one of the two channels.

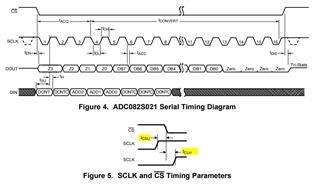

I'm looking at some logic analyzer captures to check CS and CLK timing. They have the MCU configured for CLK staying low between messages. When the Read ends, and CS goes high, the clock has just finished its 32nd pulse, meaning it has gone high then low before CS goes high. Is this acceptable?

I don't see a spec that requires the clock be high when CS goes high, but the image in figure 5 of the datasheet looks that way. Is there are requirement?

Thanks,

Darren