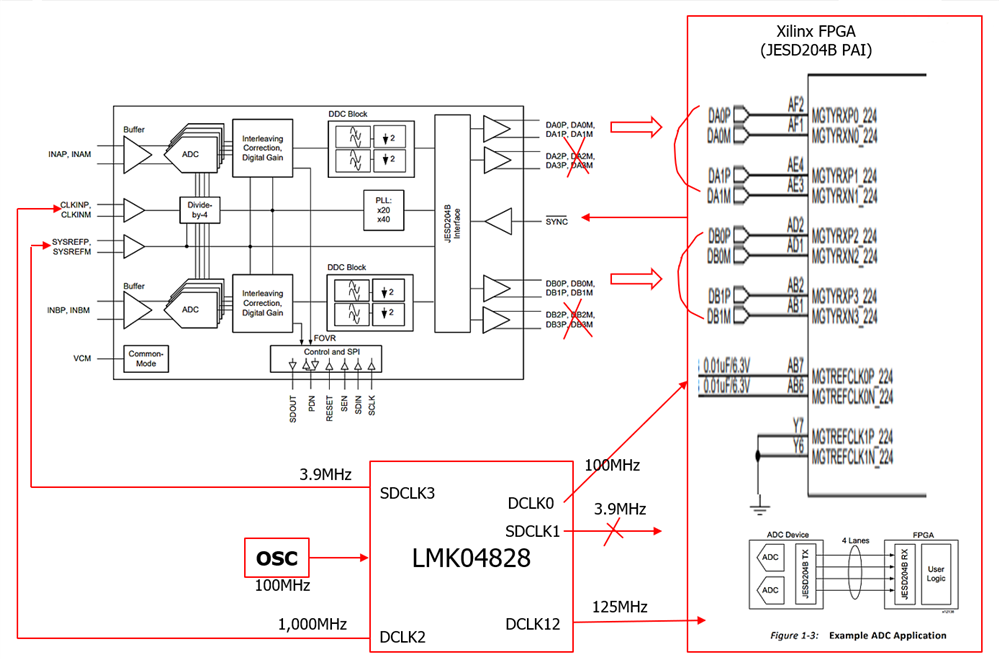

Part Number: ADS54J69

Other Parts Discussed in Thread: LMK04828

Dear TI experts,

My customer asked about ADS54J69 before, but response delays several days.

Could you check the status of this issue? The schedule is very urgent.

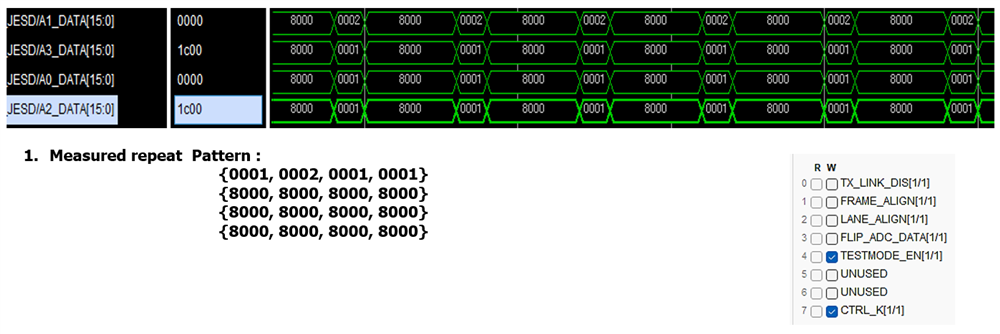

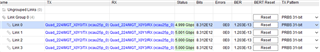

additionally, please check the other customer's project which is combined with FPGA. it would be very helpful if you give me some example about it.

Best regards,

Chase