Hello,

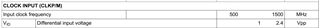

Would you clarify TI's definition of VID (differential input voltage) for the ADC34RF52 Clock input. The spec indicated

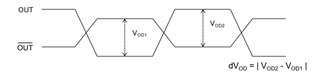

Is VID measured from signal itself as VOD seen below:

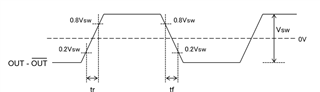

or is it measured as what is seen by the ADC's difference amp which effectively doubles the output swing when the input signals are summed:

I'm trying to determine the ratio of the step up transformer I should use to increase LVDS to approach the max spec of 2.4 Vpp

Thank you,

Joe