Hello,

My customer uses the DAC3484 with the following conditions.

- DACCLK = 1228.8MHz, Interpolation = 4x

In this case, is it correct to use OSTR = 38.4MHz and DATACLK = 614.4MHz?

Thank you.

JH

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

Hello,

My customer uses the DAC3484 with the following conditions.

- DACCLK = 1228.8MHz, Interpolation = 4x

In this case, is it correct to use OSTR = 38.4MHz and DATACLK = 614.4MHz?

Thank you.

JH

Hi JH,

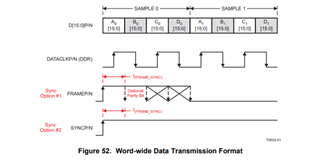

For Fdac = 1228.8MSPS, 4x interpolation, the interface rate is 368.64MSPS.

In word wide format, the total data throughput will be 4 channels X 368.64MSPS = 1228.8MSPS at 16-bits each. Since it is DDR, the clock rate for DATACLK is correct at 614.4MHz.

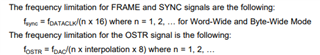

Fost = Fdac/(n*4*8) = 38.4/N, where N is integer

Yes, your calculations for dataclk of 614.4MHz and Fostr of 38.4MHz is OK.

Hi Hsia,

Thanks for your reply.

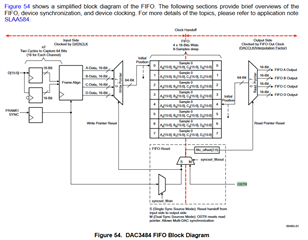

The customer encountered issue with FIFO Resync Error occurring when setting interpolation = 4x at the above clock rates. On the other hand, changing interpolation = 2x, it proceeded without Resync issue.

Please advise on debugging method to clear this issue.

Regards,

JH

Hi JH,

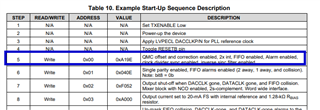

There may be a configuration issue. The example configuration is for 2x interpolation. You can adjust the INT register to accommodate for 4x interpolation.

Please also see below app note, section 2.3 for details on the FIFO optimization: