Hello TI,

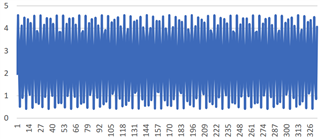

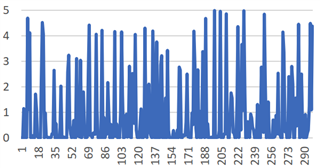

We are currently struggling with one of these component producing unexpected Data on one of our Electronic board.

Some timing issues might to be at work, but we would like some precision or confirmation we don’t find in the datasheet.

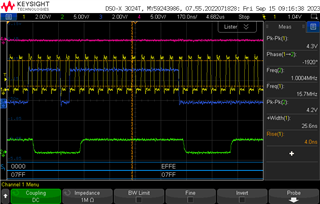

The following figure represents in red the way we are driving DIN ADC input:

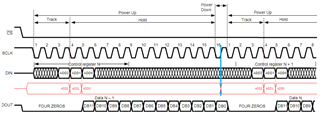

Our understanding of the datasheet was that DIN pin hold and setup timings are to be respected only for the first 8 rising edges of each 16-sclk cycle.

"While a conversion is in progress, the address of the next input for conversion is clocked into a control register

through the DIN pin on the first 8 rising edges of SCLK after the fall of CS. See Table 1, Table 2, and Table 3."

As you can see above the DIN pin (in RED) is stable for these 8 SCLK rising edge so no timing issue shall be observable there.

However we currently use the 16th SCLK rising edge (highlighted in blue) to update the DIN value for the next cycle.

Because this update happens at the same time of SCLK rising edge, we wonder whether there is a risk of setup/hold timings not being respected for control register clocking even if that happens out of the window of the first 8 rising edges.

Can this somehow lead to unexpected data output ?

Our first interpretation of the datasheet was that there was no control register clocking outside the first 8 SCLK rising edges of each 16-sclk access.

Can you confirm that point ?

Best regards,