- Ask a related questionWhat is a related question?A related question is a question created from another question. When the related question is created, it will be automatically linked to the original question.

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

Following table 18 divide by 6, when attempting to use the ADC with an LMFS setting of 4211 we are getting an output that matches what we would expect with 4244. When setting LMFS we also get the behavior of 4244. This is present both when using the ramp test pattern in the DDC block and in normal oepration.

ADC Reg Dump:

Master Page Regs:

0x20: 0x0000

0x32: 0x0000

0x39: 0x0050

0x3c: 0x0000

0x3d: 0x0005

0x57: 0x0010

0x58: 0x0000

0x5a: 0x0000

ADC Page Regs:

0x3f: 0x0000

0x42: 0x0003

Offset Correction Page Regs: (Channel A Channel B)

0x68: 0x0042 0x0042

Digital Gain Page Regs: (Channel A Channel B)

0xa6: 0x0000 0x0000

Main Digital Page Regs: (Channel A Channel B)

0x00: 0x0000 0x0000

0xa2: 0x0008 0x0008

JESD Digital Page Regs: (Channel A Channel B)

0x01: 0x0080 0x0080

0x02: 0x0000 0x0000

0x03: 0x0002 0x0002

0x04: 0x0000 0x0000

0x06: 0x0000 0x0000

0x07: 0x001f 0x001f

0x16: 0x0070 0x0070

0x17: 0x0000 0x0000

0x32: 0x0000 0x0000

0x33: 0x0000 0x0000

0x34: 0x0000 0x0000

0x35: 0x0000 0x0000

0x36: 0x0040 0x0000

0x37: 0x0002 0x0002

0x3c: 0x0001 0x0000

0x3e: 0x0060 0x0060

Decimation Filter Page Regs: (Channel A Channel B)

0x00: 0x0001 0x0001

0x01: 0x0001 0x0001

0x02: 0x0000 0x0000

0x05: 0x0001 0x0001

0x06: 0x0000 0x0000

0x07: 0x0000 0x0000

0x08: 0x0000 0x0000

0x09: 0x0000 0x0000

0x0a: 0x0000 0x0000

0x0b: 0x0000 0x0000

0x0c: 0x0000 0x0000

0x0d: 0x0000 0x0000

0x0e: 0x0000 0x0000

0x0f: 0x0000 0x0000

0x10: 0x0000 0x0000

0x11: 0x0000 0x0000

0x14: 0x0000 0x0000

0x16: 0x0000 0x0000

0x1e: 0x0041 0x0041

0x1f: 0x0001 0x0001

0x33: 0x0000 0x0000

0x34: 0x0000 0x0000

0x35: 0x0000 0x0000

0x36: 0x0000 0x0000

0x37: 0x0004 0x0004

0x3a: 0x0000 0x0000

Power Detector Page Regs: (Channel A Channel B)

0x00: 0x0000 0x0000

0x01: 0x0010 0x0010

0x02: 0x0000 0x0000

0x03: 0x0000 0x0000

0x07: 0x00e6 0x00e6

0x08: 0x00cc 0x00cc

0x09: 0x00b3 0x00b3

0x0a: 0x0099 0x0099

0x0b: 0x0000 0x0000

0x0c: 0x0000 0x0000

0x0d: 0x0000 0x0000

0x0e: 0x0000 0x0000

0x0f: 0x0000 0x0000

0x10: 0x0000 0x0000

0x11: 0x0000 0x0000

0x12: 0x0000 0x0000

0x13: 0x0000 0x0000

0x16: 0x0000 0x0000

0x17: 0x0000 0x0000

0x18: 0x0000 0x0000

0x19: 0x0000 0x0000

0x1a: 0x0000 0x0000

0x1d: 0x0000 0x0000

0x1e: 0x0000 0x0000

0x20: 0x0000 0x0000

0x21: 0x0000 0x0000

0x22: 0x0000 0x0000

0x23: 0x0000 0x0000

0x24: 0x0000 0x0000

0x25: 0x0000 0x0000

0x27: 0x0000 0x0000

0x2b: 0x0000 0x0000

0x33: 0x0005 0x0005

0x34: 0x000d 0x000d

0x35: 0x000e 0x000e

0x36: 0x000e 0x000e

0x37: 0x0000 0x0000

0x38: 0x0000 0x0000

Other notes:

Previously we were using the ADC without decimation and LMFS of 8 2 8 20. Its possible we make a mistake when converting.

Hi Doug,

Sorry for a late response today, I will try to look into this for you tomorrow!

Regards, Chase

Doug,

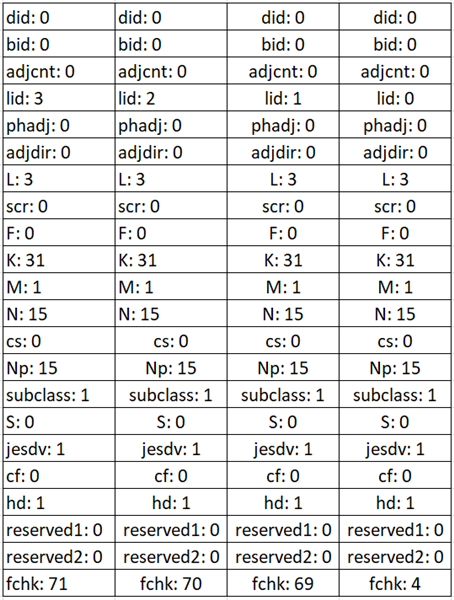

I have setup the device for this mode again (using the GUI) and see the following as the ILAS configuration data. Does this match what you are seeing? I am still working on sample unpacking for this mode to see if the samples are showing as LMFS 4211 or 4244 with this config. I will share updates when I have them.

| did: 0 | did: 0 | did: 0 | did: 0 |

| bid: 0 | bid: 0 | bid: 0 | bid: 0 |

| adjcnt: 0 | adjcnt: 0 | adjcnt: 0 | adjcnt: 0 |

| lid: 3 | lid: 2 | lid: 1 | lid: 0 |

| phadj: 0 | phadj: 0 | phadj: 0 | phadj: 0 |

| adjdir: 0 | adjdir: 0 | adjdir: 0 | adjdir: 0 |

| L: 3 | L: 3 | L: 3 | L: 3 |

| scr: 0 | scr: 0 | scr: 0 | scr: 0 |

| F: 0 | F: 0 | F: 0 | F: 0 |

| K: 31 | K: 31 | K: 31 | K: 31 |

| M: 1 | M: 1 | M: 1 | M: 1 |

| N: 15 | N: 15 | N: 15 | N: 15 |

| cs: 0 | cs: 0 | cs: 0 | cs: 0 |

| Np: 15 | Np: 15 | Np: 15 | Np: 15 |

| subclass: 1 | subclass: 1 | subclass: 1 | subclass: 1 |

| S: 0 | S: 0 | S: 0 | S: 0 |

| jesdv: 1 | jesdv: 1 | jesdv: 1 | jesdv: 1 |

| cf: 0 | cf: 0 | cf: 0 | cf: 0 |

| hd: 1 | hd: 1 | hd: 1 | hd: 1 |

| reserved1: 0 | reserved1: 0 | reserved1: 0 | reserved1: 0 |

| reserved2: 0 | reserved2: 0 | reserved2: 0 | reserved2: 0 |

| fchk: 71 | fchk: 70 | fchk: 69 | fchk: 4 |

Regards, Chase

Sorry the table above is ultra hard to read. Below is a screenshot of excel. I'm not sure why my VIO captured the checksum correct for all lanes except for lane 0. If you calculate the checksum manually, it will be correct as value 68.

Hope to update again soon.

Regards, Chase

Hi Doug,

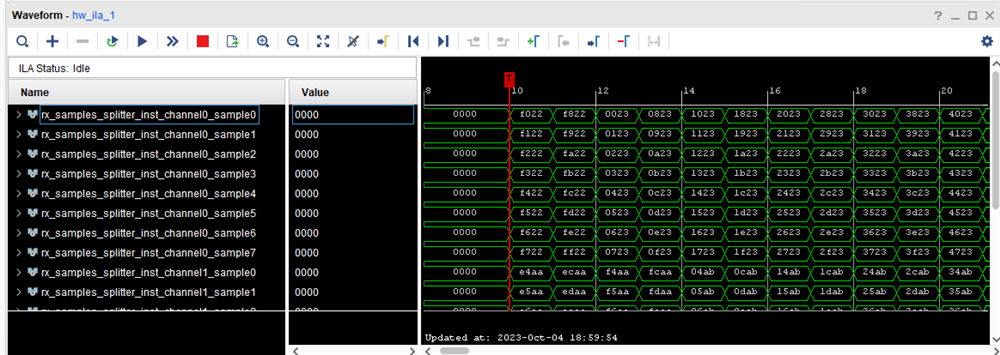

I have stayed later than usual tonight to check on this for you. I can confirm that the config that the gui makes is indeed LMFS4211. I have some lane mapping wrong in my FPGA firmware (DA1 swapped with DA2, and DB1 swapped with DB2), but I know this is 4421 for sure because this is an HD=1 mode (where samples are split across multiple lanes), and since there are only two lanes, whenever I place the ADC into ramp mode, the two bytes of the sample are swapped. Instead of the LSB incrementing, I am seeing bits 15:8 incrementing first and then bits 7:0 incrementing. This makes sense as if the lanes are swapped in 4211 mode, then the 8 MSB and the 8 LSB will be swapped per converter.

Here is the GUI configuration which I have used to test with the ADC. As it shows, I am using onboard clocking as this was the most convenient way for me to check this out. The sample rate of the ADC is 2457.6MSPS and in real ddc by 3 mode, LMFS4421, such that the output data rate = 819.2MSPS and serdes rate = 8192Mbps. Please use this to review the JESD configuration page for the converter. I have glanced at it and see that some values, such as JESD MODE 0-2 are showing a discrepancy between the GUI output (which works) and the datasheet recommendation (which seems to place the device into 4244 mode). Please try your config with these JESD settings.

RF45EVM_onboard_clk_2457p6M_LMFS4211.cfg

Regards, Chase