- Ask a related questionWhat is a related question?A related question is a question created from another question. When the related question is created, it will be automatically linked to the original question.

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

We are demonstrating a DAC using the DAC7568EVM.

The specified voltage is output, but if the update frequency is made faster, the output becomes 0.

Please tell me why the output decreases.

-SCLK clock 40MHz ・LDAC pin (DAC7568 1pin) is unused.

-Following the reset command after startup, internal reference power ON is issued.

- Ports A to G and H (SW LDAC at this timing) are updated by polling.

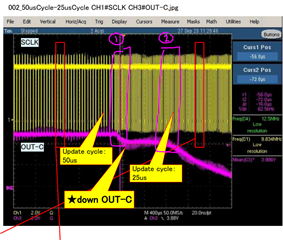

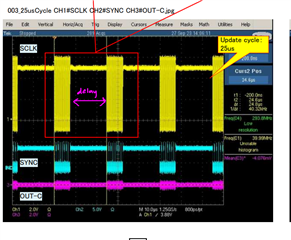

- Output when the polling cycle is 50us. - If the polling cycle is 25us, the output will drop to 0 level.

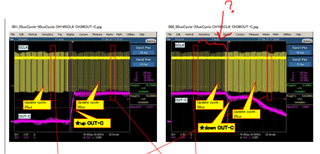

-The attached data 001_25usCycle-50usCycle CH1#SCLK CH3#OUT-C.jpg / 002_50usCycle-25usCycle CH1#SCLK CH3#OUT-C.jpg is the waveform at that time.

-The same serial data is sent for both polling cycles of 25us and 50us.

Hi Tada-san,

What commands are being sent during the time after OUTC goes high and before OUTC starts going low?

When exactly is the frequency changing? Is it between SYNC pulses? Or during a SYNC pulse in the middle of a command?

The pdf says that this section is seeing the same result? But it looks like the device is behaving fine at the faster frequency and OUTC is not decreasing like in the first screenshots. Am I interpreting this page correctly?

Best,

Katlynne Jones

Hi

Thank you for your reply,I'll answer.

you:What commands are being sent during the time after OUTC goes high and before OUTC starts going low?

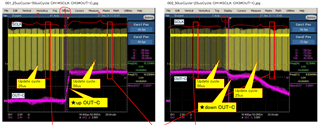

>There are no changes to the command. Only the frequency at which commands are sent has changed.see the figure below.

>The commands are the same. (Left: 25us cycle, Right: 50us cycle).However, the OUT-C level will change. (Same for OUT-A~H).

you:When exactly is the frequency changing? Is it between SYNC pulses? Or during a SYNC pulse in the middle of a command?

>The frequency switches while SYNC is High. It does not change during the Low period.

you:The pdf says that this section is seeing the same result? But it looks like the device is behaving fine at the faster frequency and OUTC is not decreasing like in the first screenshots. Am I interpreting this page correctly?

>Left and right are different cycles. However, this is a diagram that proves that it is the same command.

>The purple line is OUT-C. The figure on the left shows a command cycle of 25us, OUT-C=Low. The figure on the right shows a command cycle of 50us, OUT-C=High.

thank you for reading.

Hi Tada-san,

I misunderstood before. You are not changing the SCLK frequency, you are just changing the time between each set of 8 DAC writes. Is that correct?

Just to be sure, is every set of 8 writes in this figure using the exact same data below? Or was there different data sent at (or around) points 1 & 2 in my annotation?

Best,

Katlynne Jones

Hi

Thank you for your reply,I'll answer.

you:I misunderstood before. You are not changing the SCLK frequency, you are just changing the time between each set of 8 DAC writes. Is that correct?

>It is correct.

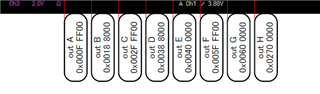

you:Just to be sure, is every set of 8 writes in this figure using the exact same data below? Or was there different data sent at (or around) points 1 & 2 in my annotation?

>All 8 write sets use exactly the same data.

Hi Tada-san,

You mentioned you are using the EVM, do you have anything else connected to the output? I will order an EVM and try to replicate this issue.

Is every channel seeing the same effects? Or is is only OUTC?

Best,

Katlynne Jones

Hi

Sorry for not noticing.Thank you for your reply,I'll answer.

you:You mentioned you are using the EVM, do you have anything else connected to the output?

>The same effect can be seen with EVM alone.

you:I will order an EVM and try to replicate this issue. Is every channel seeing the same effects? Or is is only OUTC?

>Same effect seen on all channels.

Hi

Sorry for not noticing.Thank you for your reply,I'll answer.

you:You mentioned you are using the EVM, do you have anything else connected to the output?

>The same effect can be seen with EVM alone.

you:I will order an EVM and try to replicate this issue. Is every channel seeing the same effects? Or is is only OUTC?

>Same effect seen on all channels.

Hi Tada-san,

My EVM is arriving sometime today. I will try to replicate your issue in the lab tomorrow.

Best,

Katlynne Jones

Hi

Thank you for confirming.

Could you tell me what situation after that. Have you found out anything?

Hi Tada-san,

I am unable to replicate your timing exactly to replicate the issue.

Can you share a screenshot of all writes around points 1 and 2 of my annotation. It would be good to check the writes happening right before each change in the output.

Also, is there any difference if you spread the 8 writes across the 25us polling length instead of having a large delay in between each cycle of 8 writes? This may also help us see more clearly which write is causing the output to change instead of all the 8 writes happening in sequence with no delay.

Can you also try decreasing the SPI clock speed and decreasing the delay (while keeping the total poll time 25us) to see if this makes any difference?

Best,

Katlynne Jones