Other Parts Discussed in Thread: AMC3336, AMC1336

Hi all,

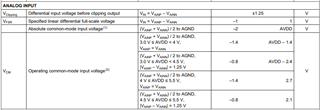

I saw similar parts (if I am right AMC3336), which require a resistive path from INN to GND. From what I understand, the AMC1336 doesn't requires to have such a path. Is it OK when I connect a 1V voltage reference to the INN pin and a signal that goes from 0 to 2V to the INP pin? Given the figure 40 of the datasheet, I would say it is permitted? Should I use a differential amplifier with 1V common mode output?

Second question was about the risks having the clock in idle mode (not clocking at all). It is mentioned that biasing current increases significantly when no clock is provided. Is there any risks not to provide a clock signal for a relatively long time (days)? What should I take in consideration for this to be OK?

Thank you.