Other Parts Discussed in Thread: AFE781H1

I am working with the TI AFE781H1 Hart Modem.

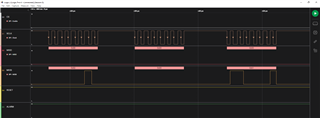

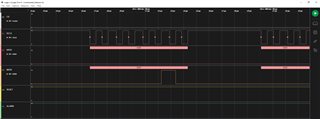

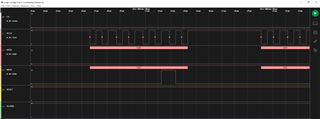

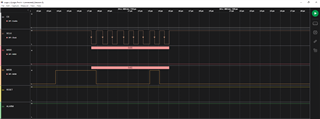

I am trying to read write to the registers in SPI Mode.

I'm using STM32U575 controller as master for the AFE.

SPI configuration parameters:

In full-duplex mode, for a 1 MHz clock speed in Mode 2,

- Clock Polarity (CPOL): 1 (Clock is high when idle)

- Clock Phase (CPHA): 0 (Data is sampled on the first edge of the clock)

- Clock Frequency: 1 MHz

- Data Order: MSB (Most Significant Bit) first

- Number of Data Bits: 8 bits

- Data Transmission Direction: Full-duplex

- Chip Select (CS) Management: Active low

setting the UART_DIS bit to 1 to disable UART, DSDO bit to 0 to enable SDO, CRC_EN bit to 0 to disable CRC in register CONFIG.

I am looking for confirmation that I am sending the correct sequence of bytes and with the correct timing.

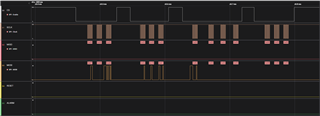

Here is my sequence:

1. doing hardware reset as per sec 7.4.2

2. Sending 3 bytes for register CONFIG (SDI = 0x02, 0x00, 0x61).

3.sending read CONFIG register value (SDI = 0x82).

4. Sending NOP command (SDI = 0x00, 0x00,0x00)

After executing this sequence, no data on SDO line.

One of my main questions is, what issue causing the SPI read register value.

Do you have any application notes besides what is in the data sheet that describes how this sequence should be done?