Other Parts Discussed in Thread: CONTROLSUITE, ADS127L01

Hi. Here i face some issue to set up the SPI communication by ADS127L01EVM (Slave) with Delfino F2833x board (Master), both are TI product.

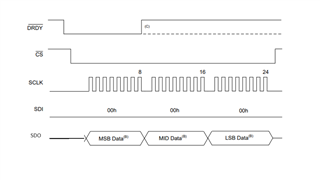

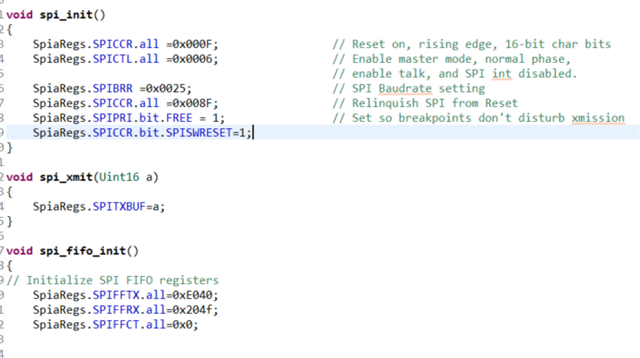

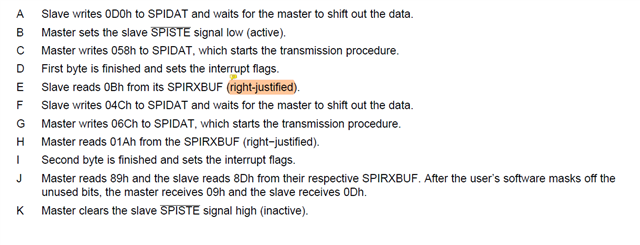

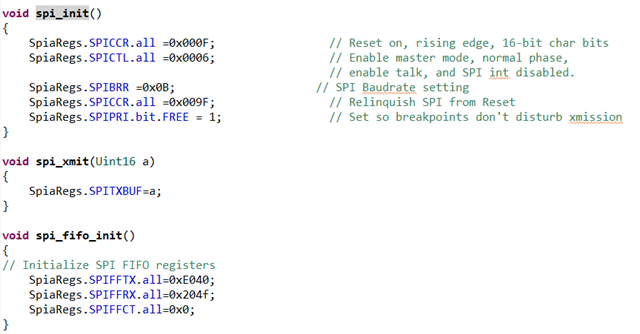

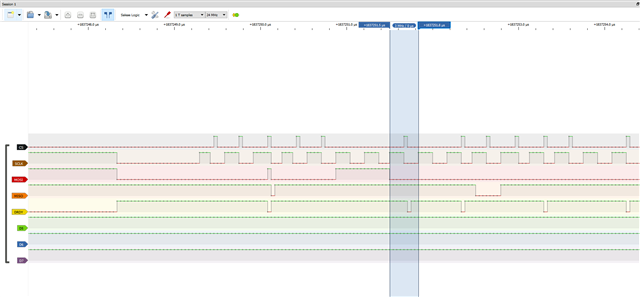

I have referred the spi_loopback code which available in "controlSUITE" and i have done the test of spi command send from Master to slave, but Master is unable to receive any information from slave. I monitor this SPI communication process with digit logic analyzer. Here i attached few pic to illustrate the SPI protocol setting.

Below are few problems that hopefuuly can get support from TI technical teams:

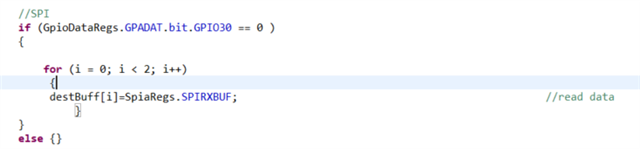

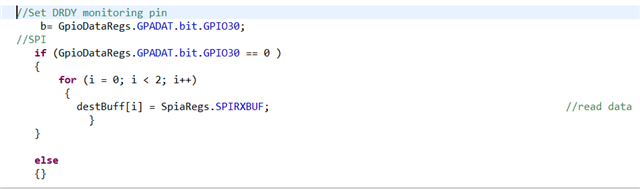

1. For the spi protocol set up with ADS127L01EVM, a input pin is needed to be set for monitoring the DRDY status, may i know is the code i show below is the right way to monitor the status of DRDY pin?

2. There are some spike happen for CS pin although i have set the CS always low in coding. Is there any issue with this phenomena and will it affect the SPI communication process? Pls see the pic attached below.

3. Based on the Question 2 pic, the SPIBFF i set is 11 but the SPI SCLK baudrate i measured is 3M Hz which is not the 150M/(SPIBFF+1) = 12.5M Hz. May i know is there any mistake i did for the setting of SPI Baudrate.