Hi,

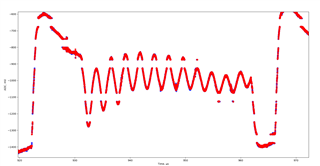

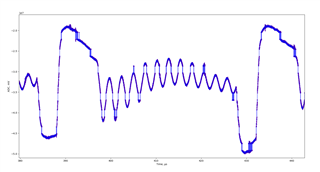

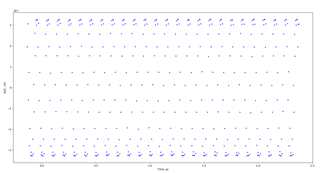

We are seeing interesting voltage jumps in our data. I've attached some captures for reference (red shows individual samples from our signal, middle blue is the signal with connecting line between samples from another capture, and last blue is a 10MHz square (or possibly sine) wave from a signal generator). Do you have any ideas on what might be wrong?

We use the following ADC configuration:

|

Register |

Value |

|

0x6 |

0x80 |

|

0x7 |

0x00 |

|

0x8 |

0x98 |

|

0xB |

0x00 |

|

0xC |

0x00 |

|

0xD |

0x6C |

|

0xE |

0x00 |

|

0xF |

0x00 |

|

0x10 |

0x00 |

|

0x11 |

0x00 |

|

0x12 |

0x00 |

|

0x13 |

0x00 |

|

0x1F |

0x7F |

|

0x26 |

0x04 |

|

0x27 |

0x03 |

|

0x2B |

0x00 |

|

0x2C |

0x00 |

|

0x2D |

0x12 |

|

0x30 |

0x40 |

|

0x36 |

0x00 |

|

0x37 |

0x00 |

|

0x38 |

0x00 |

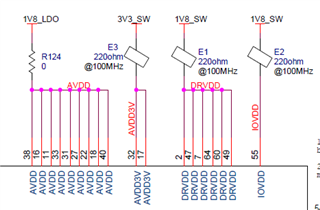

Our power source comes from an LDO (shared with other ICs) and a switcher (shared with other ICs) but separated by ferrite beads.