Hi,

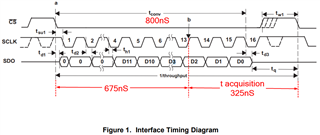

1. I was looking for detailed calculations for 1MSPS for Fsclk of 20MHz.

The value which I get is 1.25MSPS but mentioned in the datasheet is 1MSPS for 20MHz.

Can you please help me what i am missing and what calculation is involved?

2. How to calculate the filter circuit for Vkick, Vsettle?

Thank you,

Thank You.