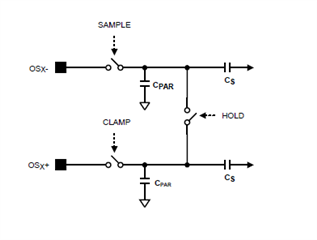

Hello, I'm reading the datasheet of the LM98640QML-SP and I found §8.2.1 a bit confusing: the name of this point is "Sample/Hold Mode", but the figure 29 description mentions "Typical CDS Mode Application Diagram". So what's exactly the configuration shown in Figure 29?

For my particular use I want to use the LM98640QML-SP to measure four 1.5V common-mode / differential outputs from a detector, therefore I would use two LM98640QML-SP and using both OS1/2+ and OS1/2- inputs for each differential output. Can you please clarify what's the application diagram I should follow in my particular case?

Thank you.