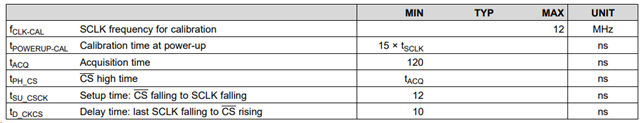

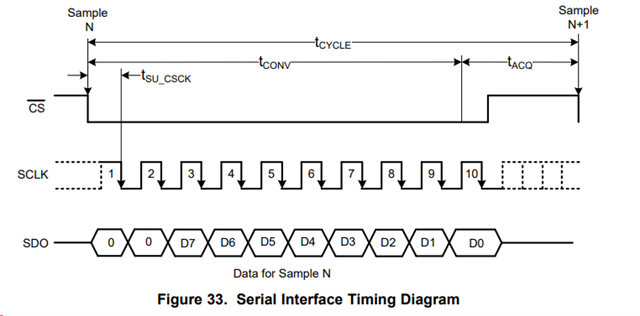

SPI timing parameters are not in the DS. When will these be documented in the datasheet?

What are the SPI clock rise/fall time min/max input requirements?

What are the SPI data input rise/fall time requirements?

What are the SPI data output rise/fall time specifications?