Other Parts Discussed in Thread: ADS124S08

Hello,

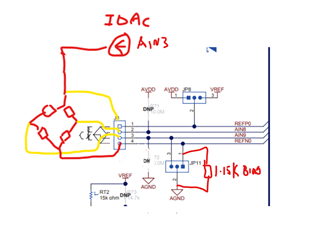

I am currently using the TI Delta Sigma Evaluation Software to evaluate the ADS124S08. We are using a full wheatstone bridge made up of 4x strain gauges. The bridge resistance is 1000 ohms. I designed the circuit as per TIs A Basic Guide to Bridge Measurements (ti.com) page 51, 6.5 Four-Wire Resistive Bridge Measurement With a Ratiometric Reference and Current Excitation.

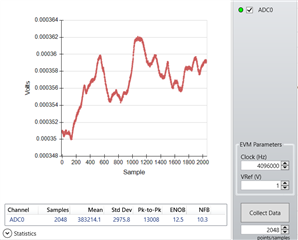

At the moment the evaluation software determines an ENOB of 12.5 bits which i think is quite low for this ADC. I was wondering if there was anyway to improve the performance or if you can spot anything glaringly wrong. .

Adc config:

20 sps

low latency filter

PGA gain of 128

IDAC 1 mA

IDAC current out of AIN3

AIN + = channel 8

AIN- = channel 9

When I run a data analysis at 1 V reference I get the following:

ENOB = 12.5 bits

Is there any way to improve this number? We would ideally like to measure down to at least 1 uV as that lets us resolve 1 uStrain.

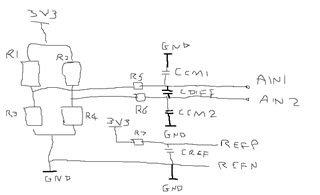

I have set up the ADC eval kit as per below:

I have configured the IDAC on AIN3 to output 1 mA.

I've modified the evaluation kit slightly in order to include a bias resistor of 1.15K between Ref N0 and GND.

I am using AIN8 as positive input and AIN9 as negative.

I measure the correct 1.65 V common mode to both inputs.

Apologies for the poor diagram below but i hope it helps illustrate my circuit.

Any help with this one is appreciated.

Kind regards