Other Parts Discussed in Thread: TLV9102, REF6050, REF5050, OPA320, ADS8860

Dear Technical Support Team,

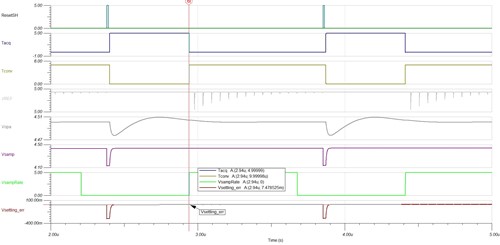

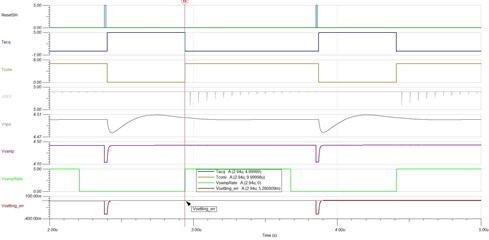

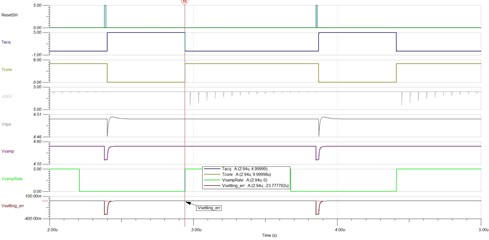

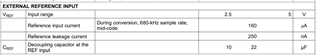

ADS8862 datasheet shows Charge-Kickback Filter and RFLT ≦22Ω and CFLT ≧590 pF(Figure 62. Charge-Kickback Filter), but my configuration is simply RC filter for ADC driver with TLV9102.

I posted for TLV9102(buffer) with R=2.2kΩ and C=2,700pF for RC filter and attached file(block diagram)

I'm confirming the phase margin and stability on followingE2E.

Attached file

I would like to confirm whether there is no problem with ADS8862 even if the configuration and constants are different between Figure 62. Charge-Kickback Filter and my board's RC filter.

Also, please let me know if you have any ideas or recommended constants for a simple RC filter.

Best Regards,

ttd