Hi,

Customers want to know how to set the sample rate of this chip? Which register to configure this function?

Do OSR (Data Output Rate) and sps mean the same thing?

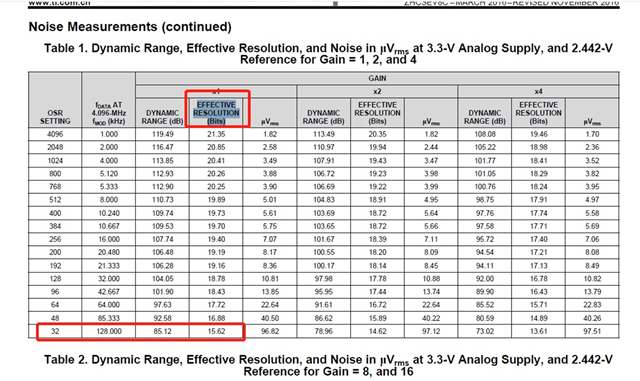

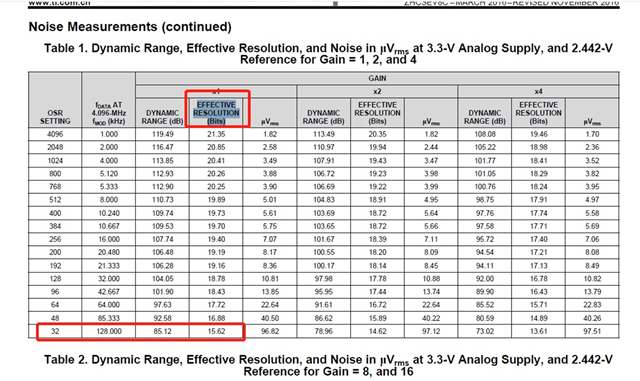

May I ask about EFFECTIVE RESOLUTION (Bits) How do you understand this?

Thanks~

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

Hi,

Customers want to know how to set the sample rate of this chip? Which register to configure this function?

Do OSR (Data Output Rate) and sps mean the same thing?

May I ask about EFFECTIVE RESOLUTION (Bits) How do you understand this?

Thanks~

Hi Rhea,

The data rate on A02 ADC is determined by the OSR and modulator frequency which is derived from ICLK and master clock. The actual data rate is confirmed as long as the OSR[3:0] and ICLK_DIV[2:0] bits in CLK2 register, CLK_DIV[2:0] bits in CLK1 register are configured. I would suggest you to check the details in the table 30, 9.3.1 lock section and also register map in A02 datasheet.

Effective resolution describes the useful bits from an analog-to-digital conversion with respect to input RMS noise. You can find the computational formula from the datasheet (equation 1).

Regards,

Dale