Hi all,

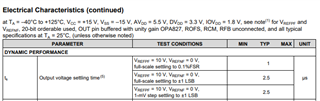

I am looking into the DAC11001A's output voltage settling time parameters. However, only the typical time is provided, and I was wondering if there is any data available for the min/max settlings times of the part based on the input conditions stated in the datasheet.

Thank you

Thank